-

Lösungen

Weitere Speicherlösungen finden Sie bei diesen Marken von Western Digital

ANSCHNALLEN, BITTE

ANSCHNALLEN, BITTECounterpoint Research schätzt, dass die Speicheranforderungen autonomer Fahrzeuge im nächsten Jahrzehnt auf 2 TB anwachsen werden

-

Innovationen

ZONED STORAGE

Deckt den Speicherbedarf von Rechenzentren durch größere Kapazität, höhere QoS und geringere TCO.

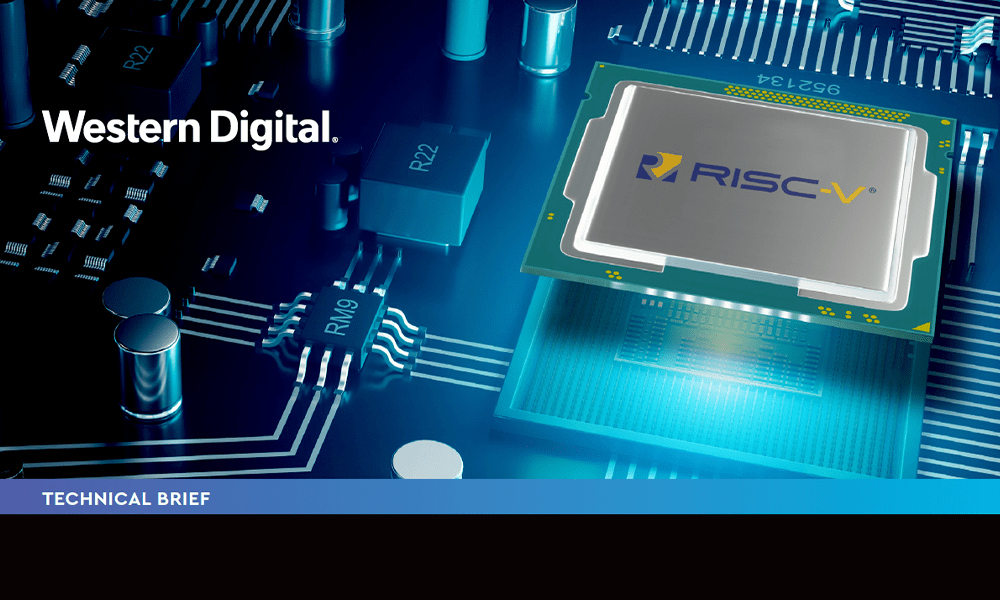

RISC-V: Mehr Geschwindigkeit für die Rechenanforderungen der

nächsten Generation

Erweiterung des RISC-V-Ökosystems

RISC-V ist eine offene Befehlsarchitektur, die eine neue Ära der Prozessorinnovation einläutet. Um die Nutzung von Schnittstellen mit offenen Standards und RISC-V-Prozessorarchitekturen weiter zu fördern, bietet Western Digital Hardware- und Softwarelösungen zur Erweiterung des RISC-V-Ökosystems.

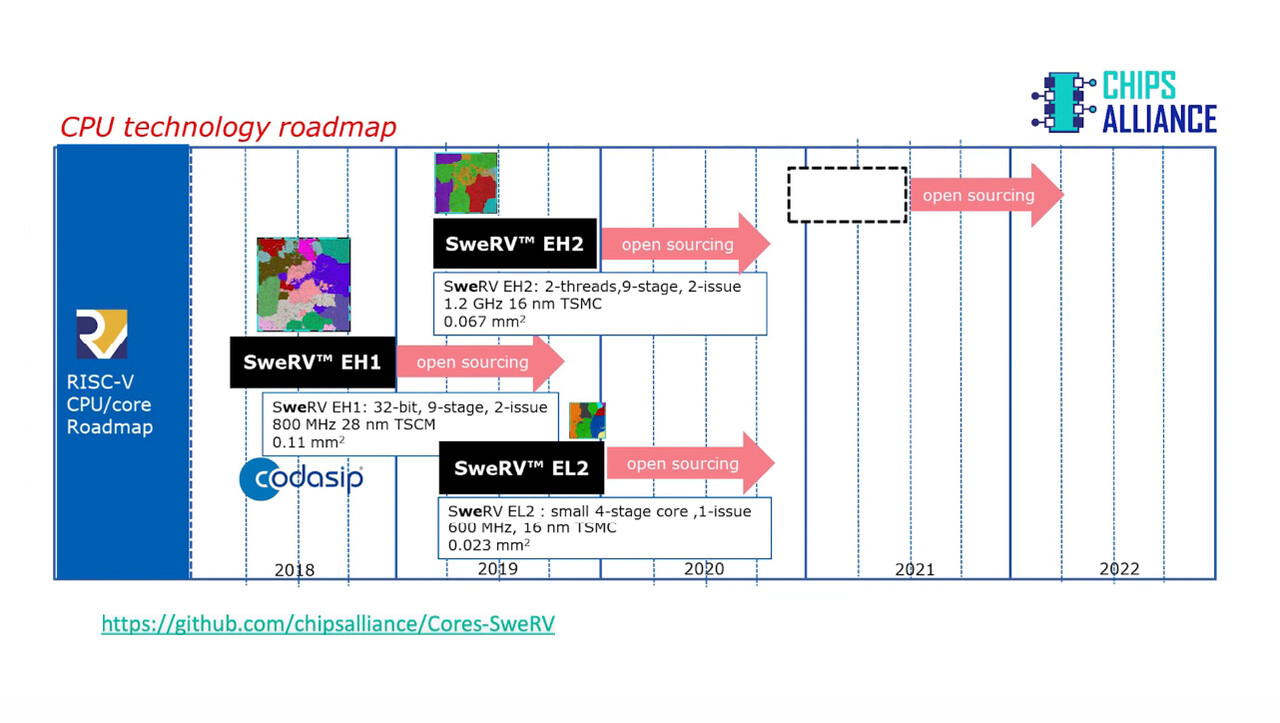

Die RISC-V SweRV CoreTM-Familie

Western Digital hat die drei RISC-V-Kerne SweRV EH1, EH2 und EL2 entwickelt.

Name des Kerns

Threads

CoreMarks/MHz

SweRV Core EH1

Single

4,9

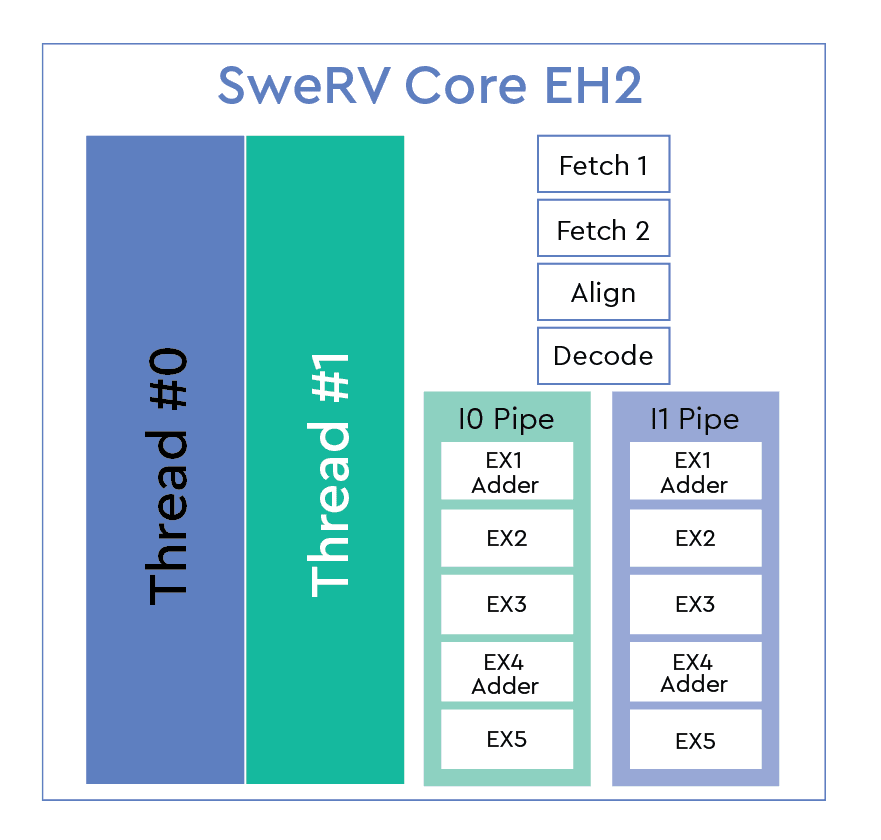

SweRV Core EH2

Dual

6,3

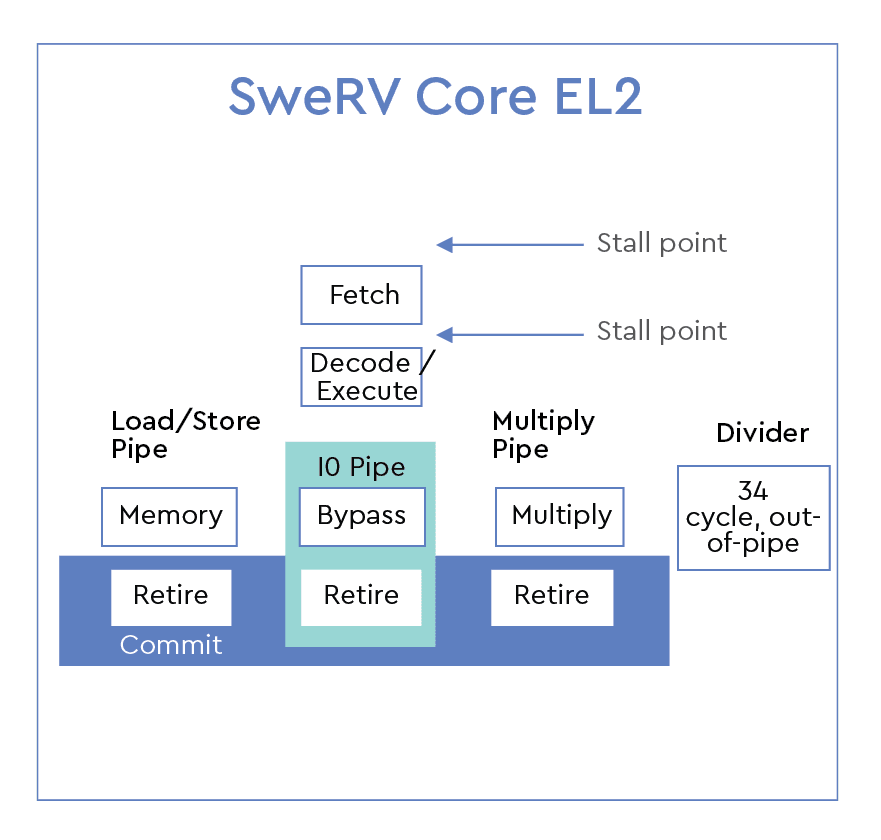

SweRV Core EL2

Single

3,6

Der Western Digital SweRV Core EH1 ist ein superskalarer und 2-Wege-assoziativer 32-Bit-Prozessorkern mit 9-stufiger Pipeline. Der SweRV Core EH2 basiert auf dem EH1, bietet jedoch durch Dual-Thread-Design mehr Leistung. Der SweRV Core EL2 ist ein kleinerer Kern mit mittlerer Leistung. Er wurde entwickelt, um in SoCs State Machines und andere Logikfunktionen zu ersetzen.

Die SweRV Cores werden in naher Zukunft in verschiedenen Western Digital Produkten zum Einsatz kommen. Alle drei Kerne basieren auf Open-Source-Angeboten von CHIPS Alliance Github. CHIPS Alliance ist eine Organisation, die Open-Source-Hardware und Open-Source-Softwaredesigntools entwickelt. Es handelt sich um eine barrierefreie kollaborative Umgebung, die die Kosten der RTL-Entwicklung senkt. Der SweRV Core EH1 ist unter https://github.com/chipsalliance/Cores-SweRV verfügbar.

Der EH2 hier: https://github.com/chipsalliance/Cores-SweRV-EH2

Und der EL2 hier: https://github.com/chipsalliance/Cores-SweRV-EL2

Video

RISC-V SweRV Core-Familie – Übersicht

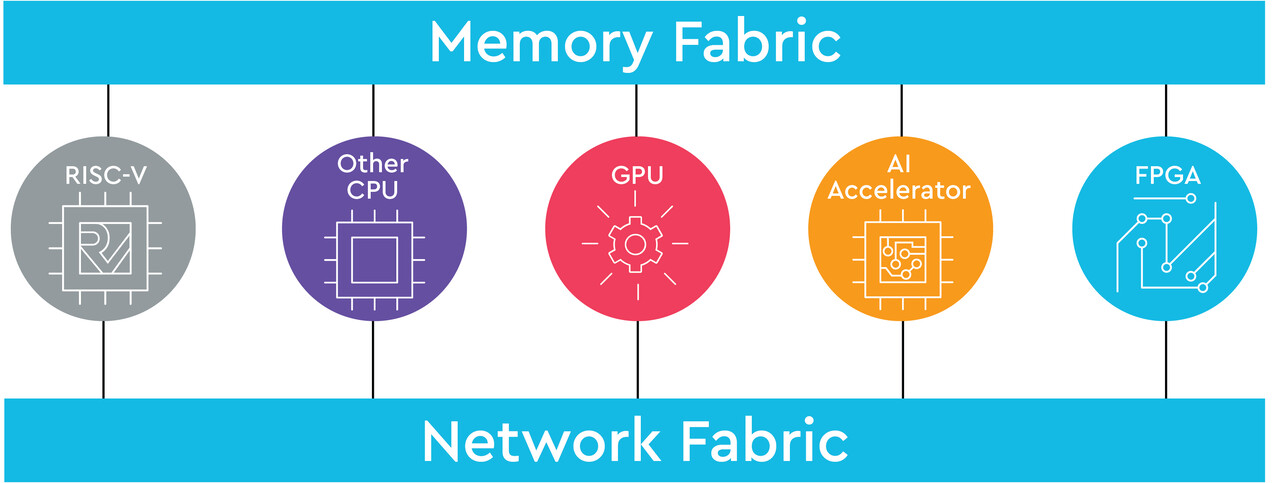

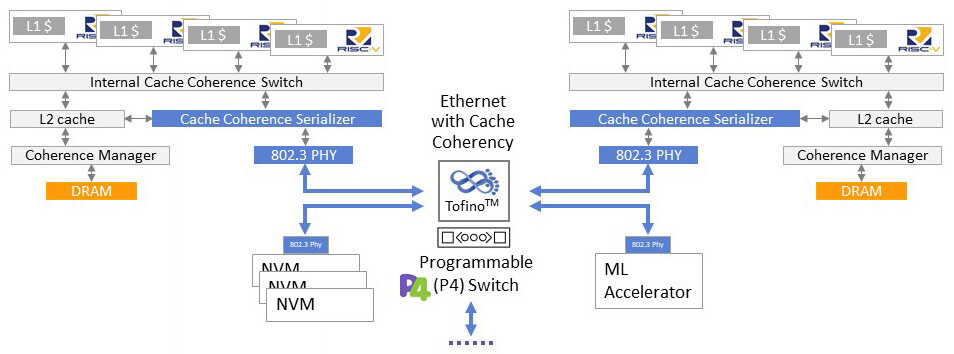

OmniXtend: Direct to Caches über Commodity Fabric

OmniXtend von Western Digital ist ein offenes Cache-Kohärenzprotokoll, das die Programmierbarkeit moderner Ethernet-Switches nutzt, um Prozessor-Caches, Speichercontrollern und Beschleunigern den direkten Austausch von Koheränzinformationen über ein Ethernet-kompatibles Fabric-Modul zu ermöglichen. Es handelt sich um eine vollständig offene Lösung zum effizienten Anschließen von persistentem Speicher an Prozessoren mit potenzieller Unterstützung für zukünftige Netzwerkstrukturen, die Rechen-, Massenspeicher-, Arbeitsspeicher- und E/A-Komponenten miteinander verbinden.

OmniXtend nutzt das TileLink-Kohärenzprotokoll zur Skalierung über den Prozessorchip hinaus. Die Programmierbarkeit der Dataplane von OmniXtend ermöglicht zukünftige Optimierungen des Protokolls unmittelbar im Feld, ohne dass dazu neue Systemsoftware oder neue ASICs benötigt werden. OmniXtend wird innerhalb der CHIPS Alliance Organisation weiterentwickelt. Weitere Informationen finden Sie unter https://github.com/chipsalliance/omnixtend.

Video

Strategische Innovation: RISC-V bei Western Digital®

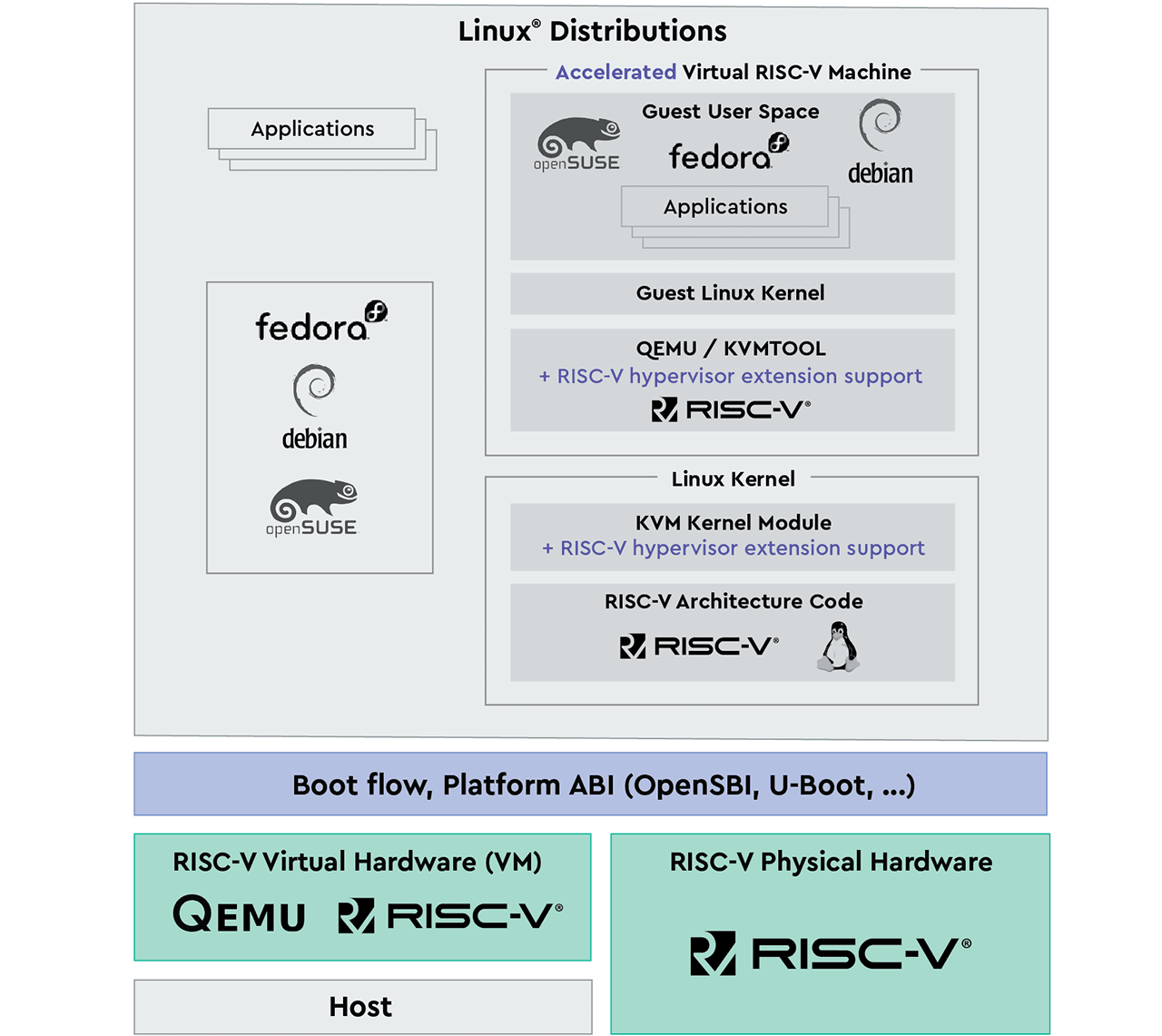

Open-Source-RISC-V-Software

RISC-V benötigt ein komplettes Software-Ökosystem, um optimal zu funktionieren. Die Komponenten dieses Ökosystems sind zahlreich und sehr unterschiedlich. Sie erstrecken sich über alle Layer von Low-Level-Firmware und Bootloadern bis zu voll funktionalen Betriebssystemkerneln und Anwendungen. Jede der Komponenten ist für den Erfolg von RISC-V unverzichtbar. Die besondere Dynamik der Open-Source-Beiträge beschleunigt die Entwicklung.

Um Innovationen im Ökosystem voranzutreiben, hat Western Digital verschiedene Beiträge zur Linux-Community geleistet. Weitere Informationen hierzu finden Sie auf https://github.com/kvm-riscv.

Ausgewählte Downloads

Wenn Sie benötigte Informationen ungehindert abrufen können, eröffnen sich unendliche Möglichkeiten. Beschleunigen Sie Ihre Datenflüsse und schöpfen Sie das volle Potenzial Ihrer Daten aus.

Innovationen für eine datenzentrische Welt

Video

RISC-V Summit 2019: Speicher entfesselt!

15. Januar 2020

Western Digital stellt in seiner 2019 RISC-V Summit-Keynote die neuen SweRV Cores und das OmniXtend-Referenzdesign vor

Video

RISC-V Summit 2019:

RISC-V und Chips Alliance zu aktuellen Anforderungen bei der Rechenleistung

15. Januar 2020

CHIPS Alliance-Keynote auf dem 2019 RISC-V Summit mit Vorstellung der Organisation und Informationen zu aktuellen Entwicklungen.

Video

RISC-V Summit 2019: Eine offene und kohärente speicherzentrische Architektur auf Basis von RISC-V

15. Januar 2020

Technisches Update zu OmniXtend, einem Cache-kohärenten Ethernet-basiertem Speicher-Fabric

Video

RISC-V Summit 2019: Roadmap der SweRV Cores

15. Januar 2020

Technische Details zu den neuen RISC-V SweRV Core EH2 und EL2 von Western Digital.

Video

RISC-V Summit 2019: Hauptsponsor Western Digital stellt GCC Compiler Code Size Density vor

15. Januar 2020

Die neuesten GCC Code-Density-Verbesserungen für RISC-V.

Video

RISC-V Summit 2019: Hauptsponsor Western Digital präsentiert RISC V Hypervisor-Unterstützung.

15. Januar 2020

Technisches Update zu QEMU- und Hypervisor-Unterstützung für RISC-V.

Veranstaltung

RISC-V-Veranstaltungen

4. April 2019

Die RISC-V Foundation hält regelmäßig Veranstaltungen und Workshops ab. Nehmen Sie an einer Veranstaltung in Ihrer Nähe teil.

Video

OmniXtend, ein kohärenter Open-Cache-Speicher-Fabric

12. Juni 2019

Umfassende Übersicht über Western Digital OmniXtend. Direct to Caches über Commodity Ethernet-Fabric Mit diesem offenen Cache-Kohärenzbus können heterogene Geräte in gleicher Weise auf den Hauptspeicher zugreifen.

Video

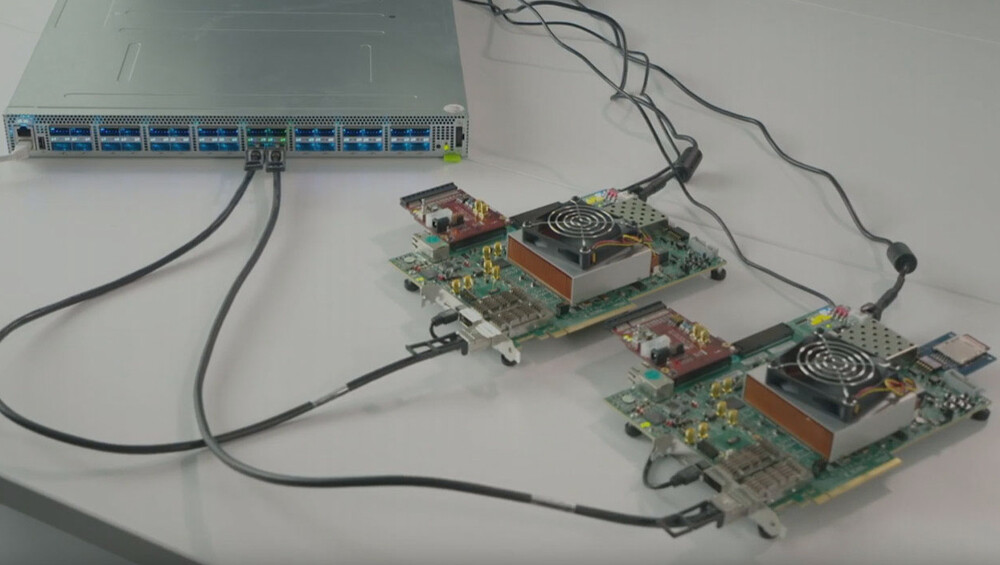

Demo zur Einrichtung des kohärenten Speicher-Fabrics OmniXtend mit RISC-V und Tofino

20. Juni 2019

Video mit detaillierter Erläuterung zur Einrichtung eines OmniXtend-Demo. Dieses Demo nutzt zwei FPGA-Boards und einen programmierbaren Ethernet-Switch. Es erläutert die Programmierung der FPGA-Boards und den P4-Code, der auf dem Switch ausgeführt werden muss.

Artikel aus unserem Blog

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

WeiterlesenSind Sie an

RISC-V interessiert?

Lassen Sie uns Kontakt aufnehmen.

Angaben

1. Basierend auf unternehmensinternen Tests