-

Solutions

Secteurs

Cas d'utilisation

Pour des solutions de stockage personnel, découvrez ces marques Western Digital

ACCROCHEZ-VOUS

ACCROCHEZ-VOUSLa société Counterpoint Research a estimé que la capacité de stockage requise pour les véhicules autonomes dépassera les 2 To au cours des dix prochaines années

-

Innovations

Pour une nouvelle ère d'architectures informatiques ouvertes centrées sur les données.

ZONED STORAGE

Cette solution est adaptée à l'échelle des datacenters, leur offrant ainsi une capacité accrue et une qualité de service supérieure, le tout avec un coût total de possession inférieur

RISC-V : accélération des besoins informatiques de

prochaine génération

Développement d'un écosystème RISC-V

RISC-V est une architecture de jeu d'instructions open source qui ouvre la voie à des innovations dans le traitement des données. Afin d'accélérer davantage le développement des interfaces standard ouvertes et des architectures de traitement RISC-V, Western Digital a contribué au développement de solutions matérielles et logicielles afin de favoriser la croissance de l'écosystème RISC-V.

La gamme SweRV CoreTM RISC-V

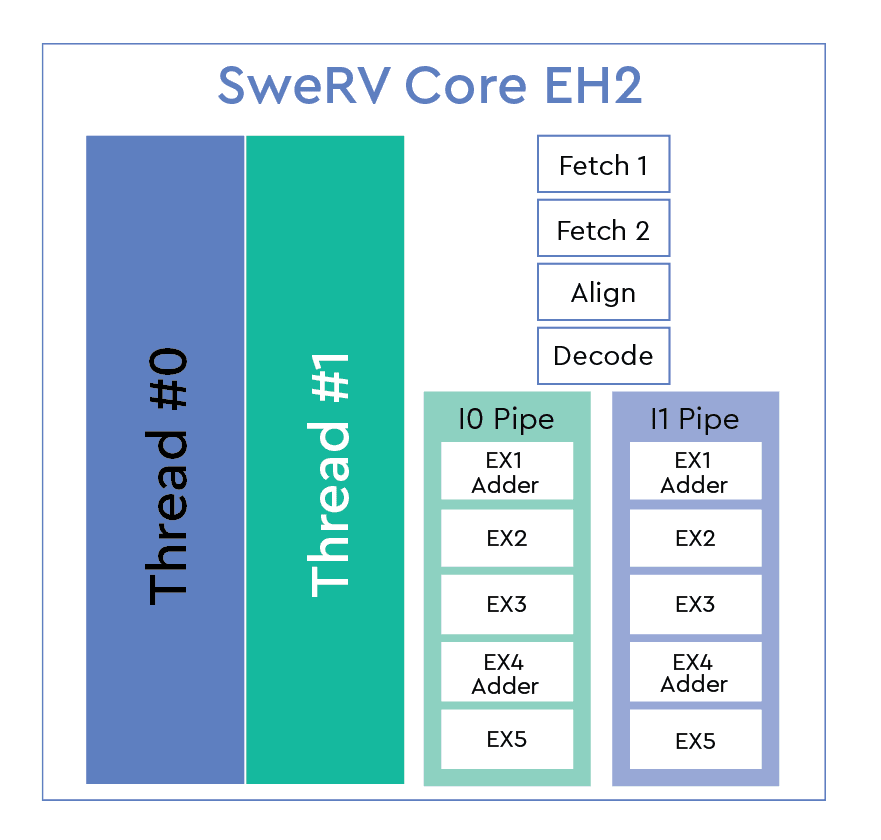

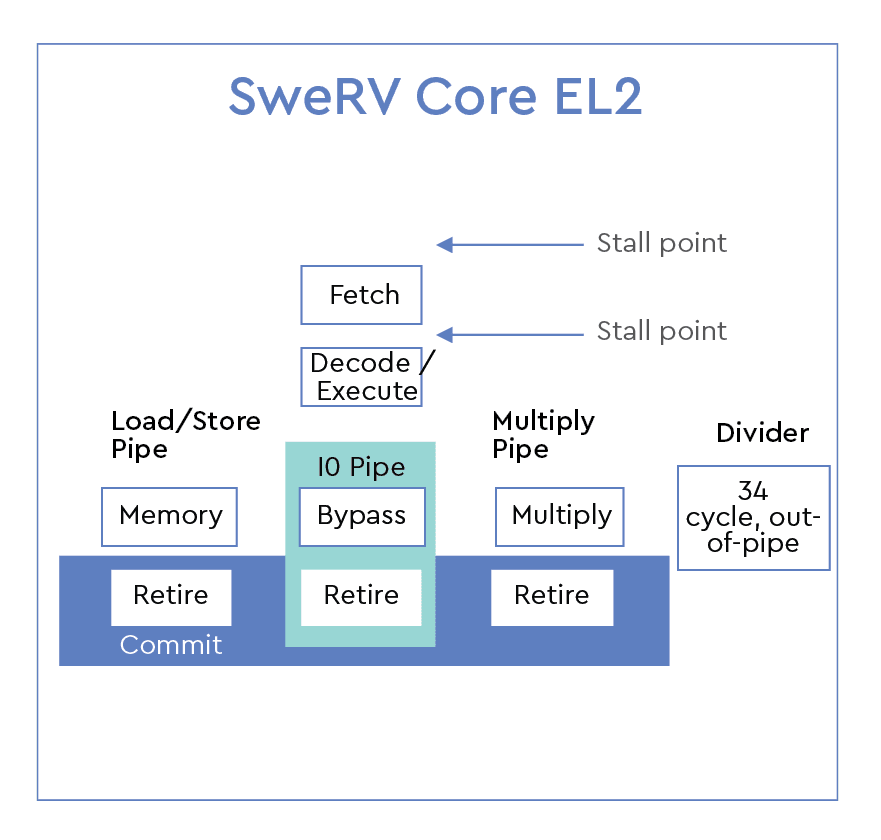

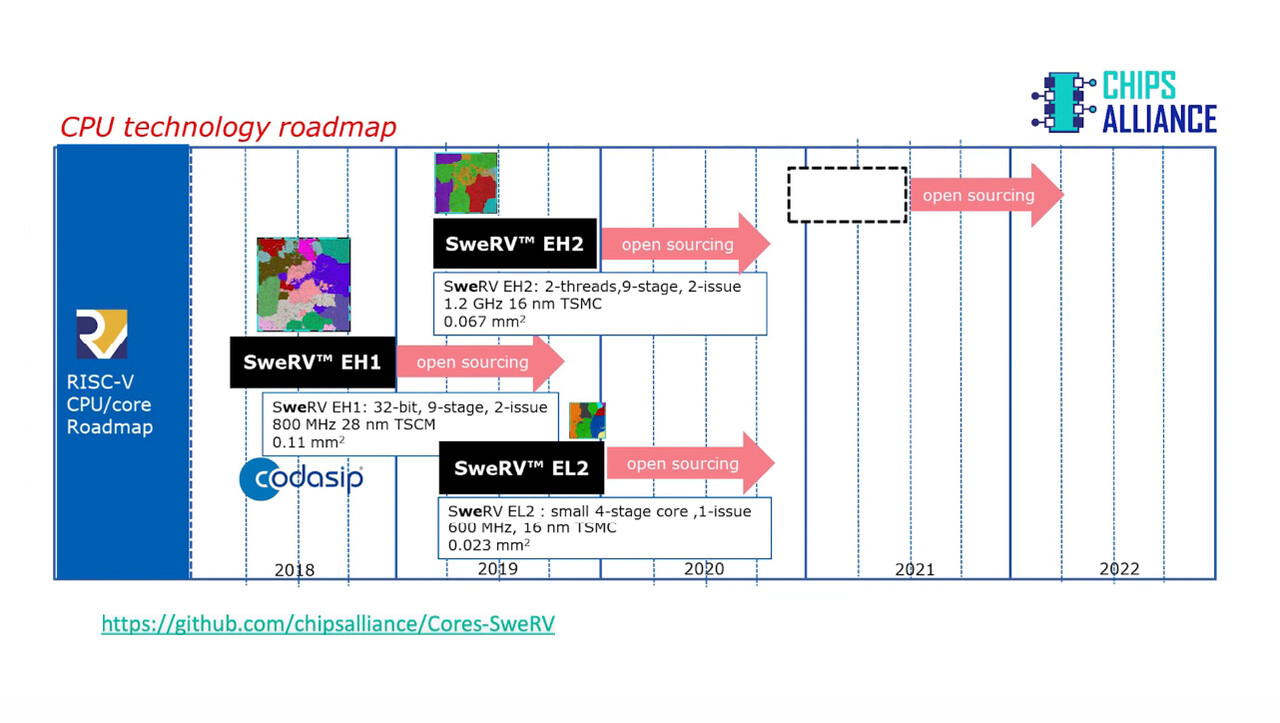

Western Digital a développé trois coeurs RISC-V : le SweRV Core EH1, EH2 et EL2.

Nom du coeur

Threads

CoreMark/MHz

SweRV Core EH1

Unique

4,9

SweRV Core EH2

Double

6,3

SweRV Core EL2

Unique

3,6

Le SweRV Core EH1 de Western Digital est un coeur 32 bits superscalaire de degré 2 doté d'un pipeline de neuf étages. Le SweRV Core EH2 se base sur le EH1, mais dispose de deux threads pour plus de performances. Pour finir, le SweRV Core EL2 est un coeur plus petit offrant une puissance moyenne. Il est conçu pour remplacer les machines à état et d'autres composants logiques dans les systèmes sur puce.

Les coeurs SweRV seront prochainement intégrés dans de nombreux produits Western Digital. Les trois coeurs ont été mis en open source dans le github du projet CHIPS Alliance. CHIPS Alliance est une organisation qui développe du matériel et des outils de conception de logiciels en open source. Il s'agit d'un environnement collaboratif sans obstacle qui réduit les coûts de développement RTL (register transfer level). Le cœur SweRV EH1 est disponible sur la page https://github.com/chipsalliance/Cores-SweRV

L'EH2 est disponible sur la page https://github.com/chipsalliance/Cores-SweRV-EH2

Et l'EL2 est disponible sur la page https://github.com/chipsalliance/Cores-SweRV-EL2

Vidéo

Présentation de la gamme de coeurs SweRV RISC-V

OmniXtend : direct to Caches over Commodity Fabric (Connexion directe aux caches sur une structure de base)

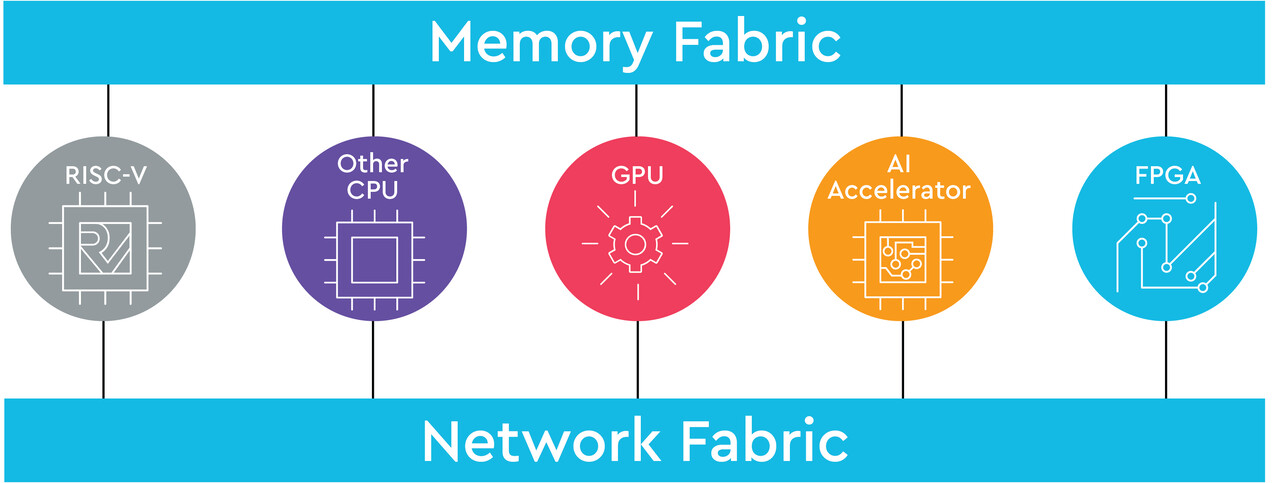

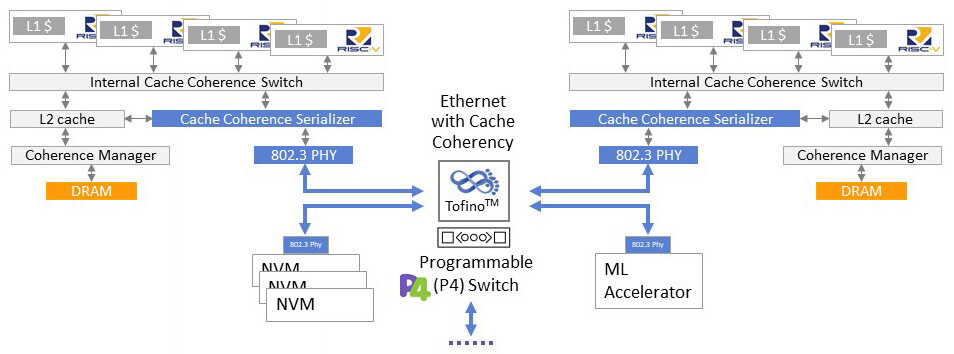

OmniXtend de Western Digital est un protocole de cohérence de cache ouvert qui utilise la programmabilité des commutateurs Ethernet modernes pour permettre aux caches des processeurs, aux contrôleurs de mémoire et aux accélérateurs d'échanger des messages de cohérence directement sur une structure compatible Ethernet. Il s’agit d’une solution complètement ouverte permettant de relier efficacement la mémoire persistante aux processeurs ; elle offre en outre la possibilité de prendre en charge les futurs maillages avancés qui relieront les composants de calcul, de stockage, de mémoire et d’E/S.

OmniXtend s'appuie sur le protocole de cohérence TileLink afin d'évoluer au-delà de la puce de processeur. La programmabilité du plan de données OmniXtend permet de déployer immédiatement les prochaines améliorations du protocole sur le terrain, sans avoir recours à de nouveaux logiciels système ou de nouveaux ASIC. De nouveaux développements d'OmniXtend seront effectués au sein de l'organisation CHIPS Alliance. Vous trouverez davantage d'informations sur la page https://github.com/chipsalliance/omnixtend.

Vidéo

Innovation stratégique : RISC-V chez Western Digital

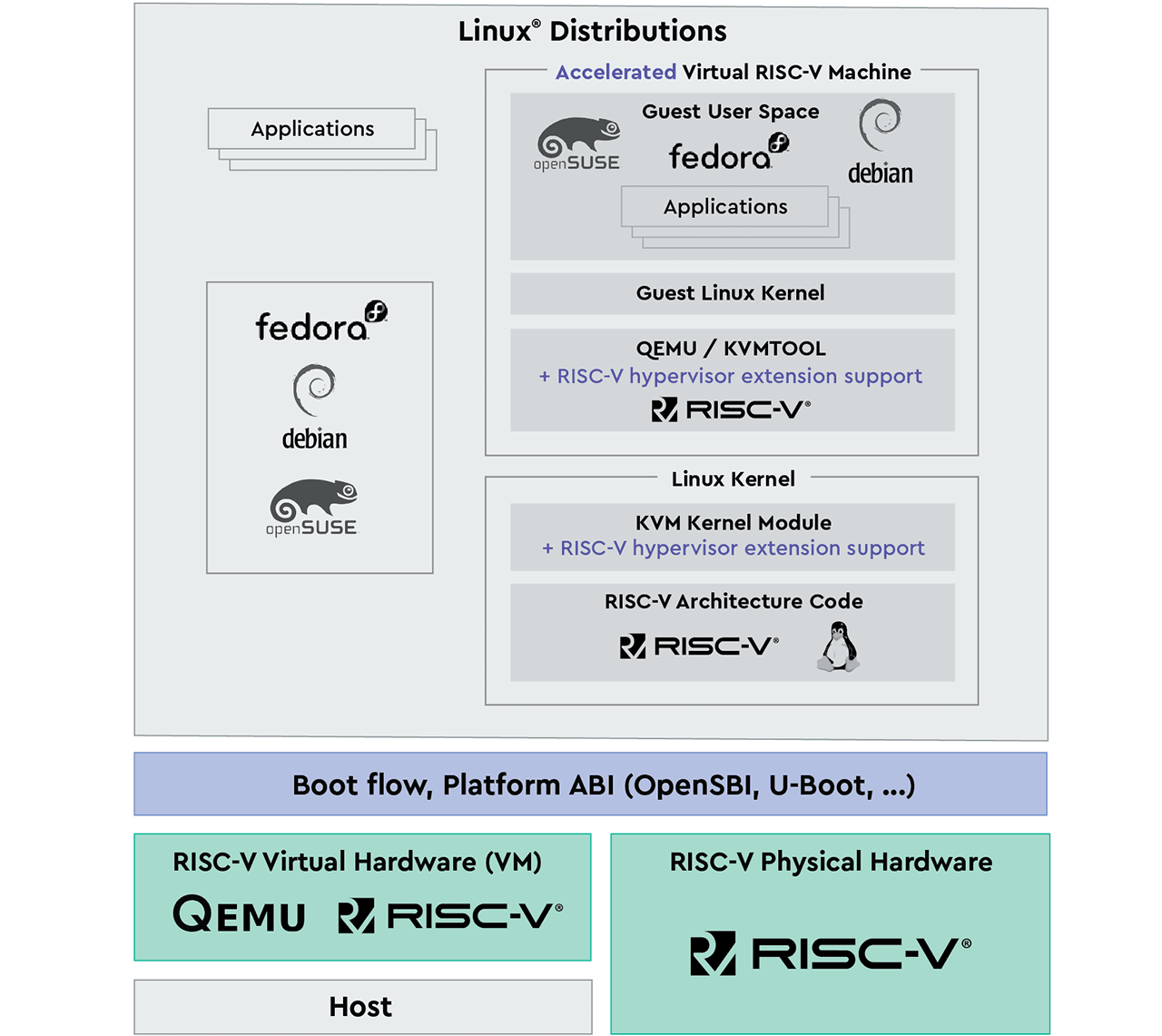

Logiciel RISC-V open source

L'architecture RISC-V aura besoin d'évoluer dans un écosystème logiciel complet pour se développer. Les composants de l'écosystème sont très divers, s'étendant à toutes les couches depuis le micrologiciel de bas niveau et les chargeurs de démarrage jusqu'aux applications et au noyau de système d'exploitation entièrement fonctionnel. Chacun de ces composants est important pour assurer le succès de l'architecture RISC-V. De plus, la puissance des contributions open source accélère la construction.

Afin d'encourager les innovations au sein de l'écosystème, Western Digital a apporté de nombreuses contributions à la communauté Linux. Des informations supplémentaires sont disponibles sur la page suivante https://github.com/kvm-riscv.

Téléchargements en vedette

Lorsque vous avez accès aux informations, les possibilités sont infinies. Accélérez le flux de vos données pour qu'elles puissent croître sans limites.

Des innovations pour un monde centré sur les données

Vidéo

RISC-V Summit 2019 : libération de la mémoire !

15 janvier 2020

Conférence de Western Digital au RISC-V Summit 2019 annonçant de nouveaux cœurs SweRV et la conception de référence OmniXtend

Vidéo

RISC-V Summit 2019 :

RISC-V et la Chips Alliance répondent aux nouvelles exigences informatiques

15 janvier 2020

Conférence de la CHIPS Alliance au RISC-V Summit 2019 : explications relatives à l'organisation et aux derniers efforts de développement.

Vidéo

RISC-V Summit 2019 : Une architecture ouverte et cohérente centrée sur la mémoire grâce au RISC-V

15 janvier 2020

Mise à jour technique de OmniXtend, une structure de mémoire basée sur Ethernet pour la cohérence de cache.

Vidéo

RISC-V Summit 2019 : Feuille de route des coeurs SweR

15 janvier 2020

Informations techniques sur les nouveaux coeurs RISC-V : SweRV Core EH2 et EL2 de Western Digital

Vidéo

RISC-V Summit 2019 : Western Digital, le sponsor principal, présente la densité de taille du code généré par le compilateur GCC

15 janvier 2020

Les dernières améliorations en termes de densité du code compilé avec GCC pour RISC-V.

Vidéo

RISC-V Summit 2019 : Western Digital, le sponsor principal, présente la prise en charge de l'hyperviseur RISC-V

15 janvier 2020

Mise à jour technique sur la prise en charge de l'hyperviseur et de QEMU pour RISC-V.

Événement

Événements RISC-V

4 avril 2019

La RISC-V Foundation organise régulièrement des événements et des ateliers. Participez à un événement près de chez vous.

Vidéo

OmniXtend, une structure de mémoire ouverte pour la cohérence du cache

12 juin 2019

Une présentation détaillée de OmniXtend de Western Digital A direct to caches over commodity Ethernet fabric (Une connexion directe aux caches sur une structure Ethernet de base). Grâce à ce bus à structure ouverte pour la cohérence du cache, des dispositifs hétérogènes peuvent désormais accéder à la mémoire principale de la même façon.

Vidéo

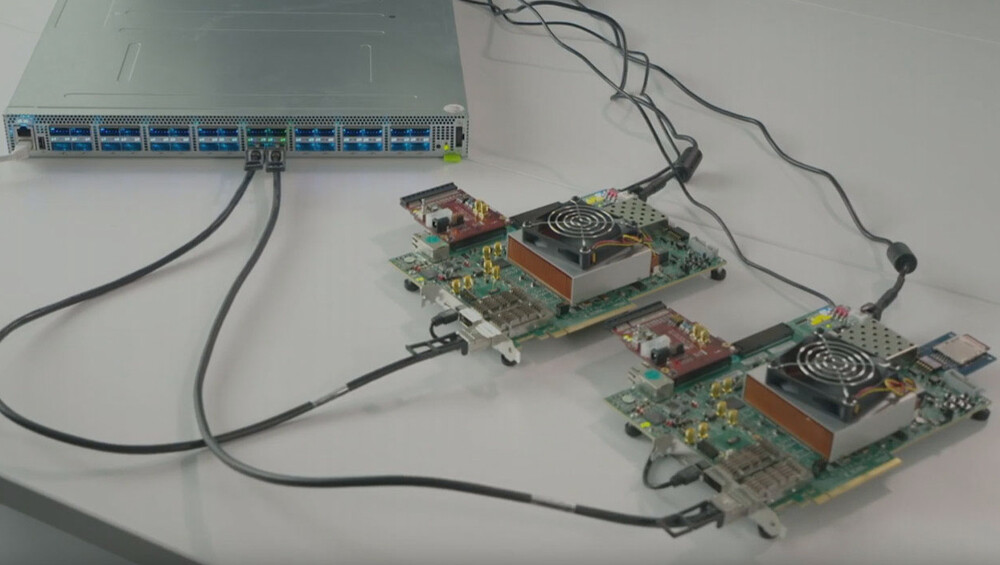

Démonstration de la configuration d’une structure de mémoire pour la cohérence OmniXtend avec RISC-V et Tofino

20 juin 2019

Une vidéo détaillée expliquant comment configurer une démo OmniXtend. Cette démo utilise deux cartes FPGA et un commutateur Ethernet programmable. Elle explique comment programmer les cartes FPGA et le code P4 nécessaires pour fonctionner sur le commutateur.

Articles en vedette de notre blog

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

En savoir plusÊtes-vous intéressé par le

RISC-V ?

Contactez-nous !

Avertissements

1. Basé sur des tests internes.