RISC-V:

次世代の

コンピューティング要件を加速

ますます拡大するRISC-Vエコシステム

RISC-Vは新時代のプロセッサイノベーションを実現するオープンISAです。オープンスタンダードインターフェイスとRISC-V処理アーキテクチャをさらに使いやすいものにするために、Western DigitalはRISC-Vエコシステムの拡大をサポートするハードウェアおよびソフトウェアソリューションを提供しています。

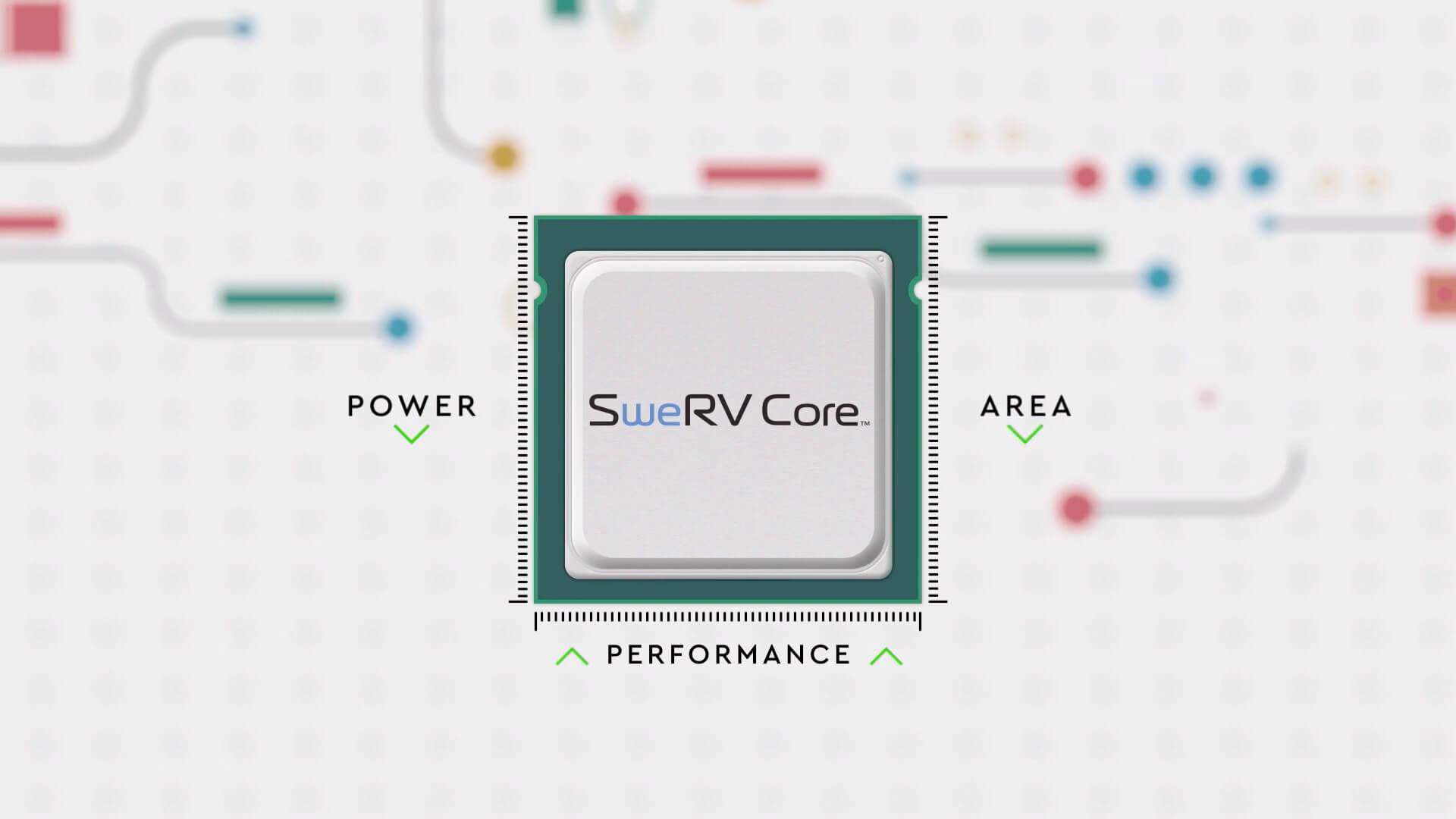

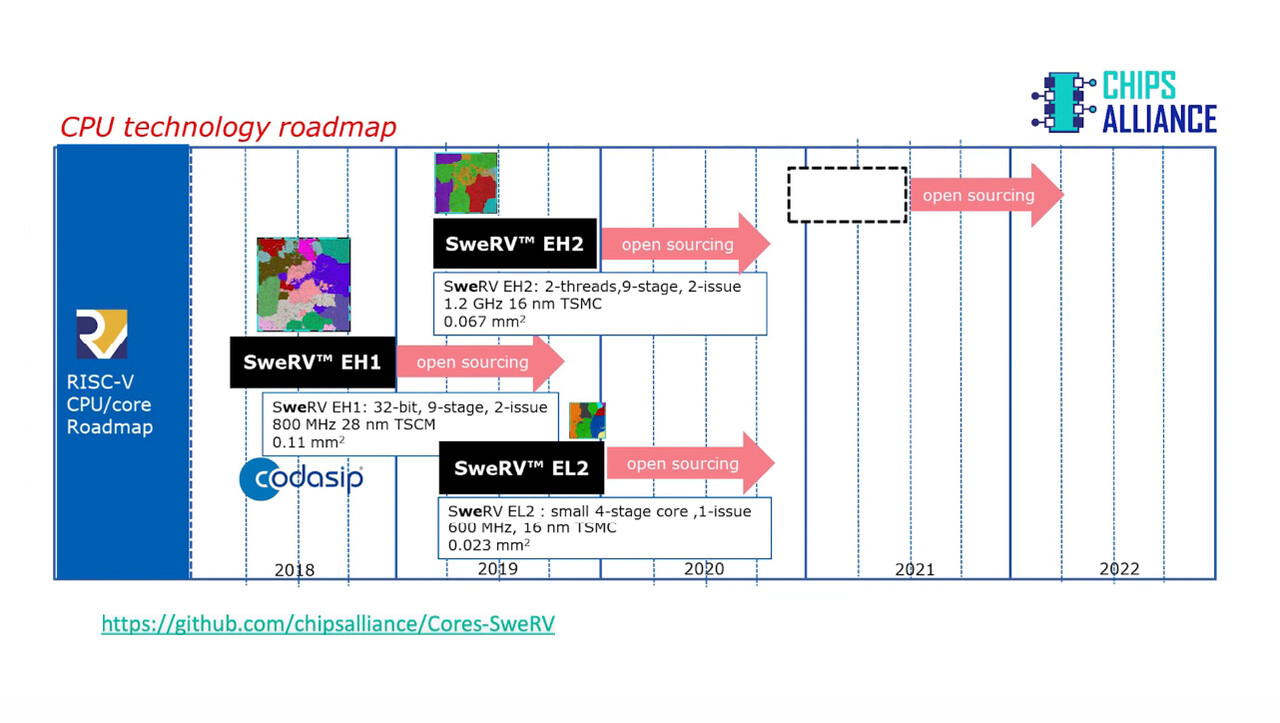

RISC-V SweRV CoreTMファミリー

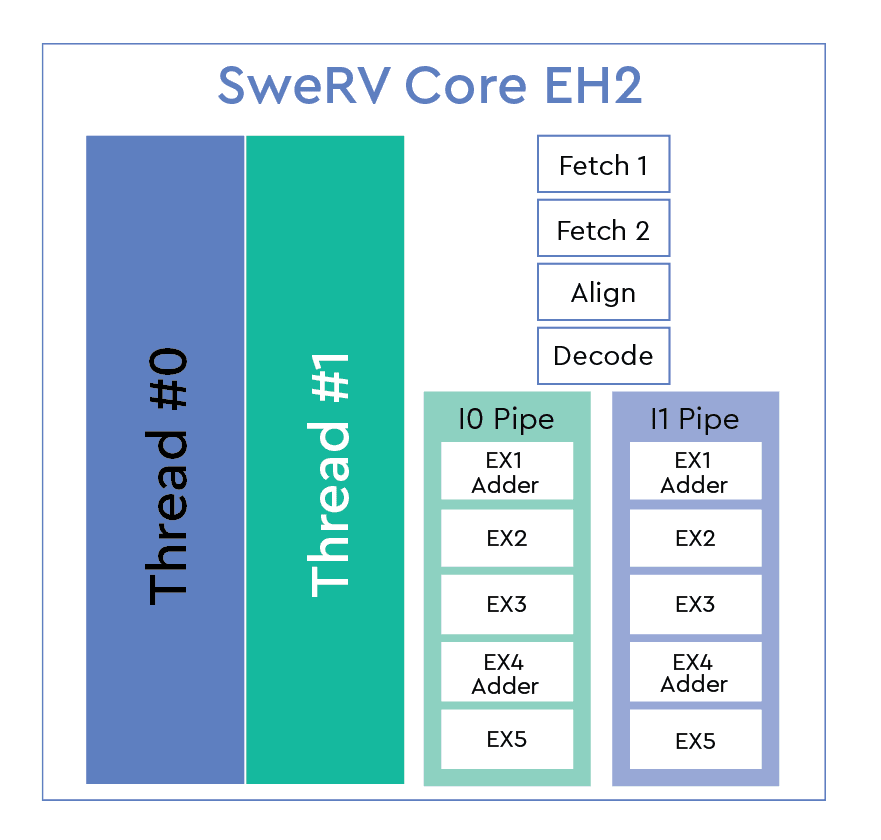

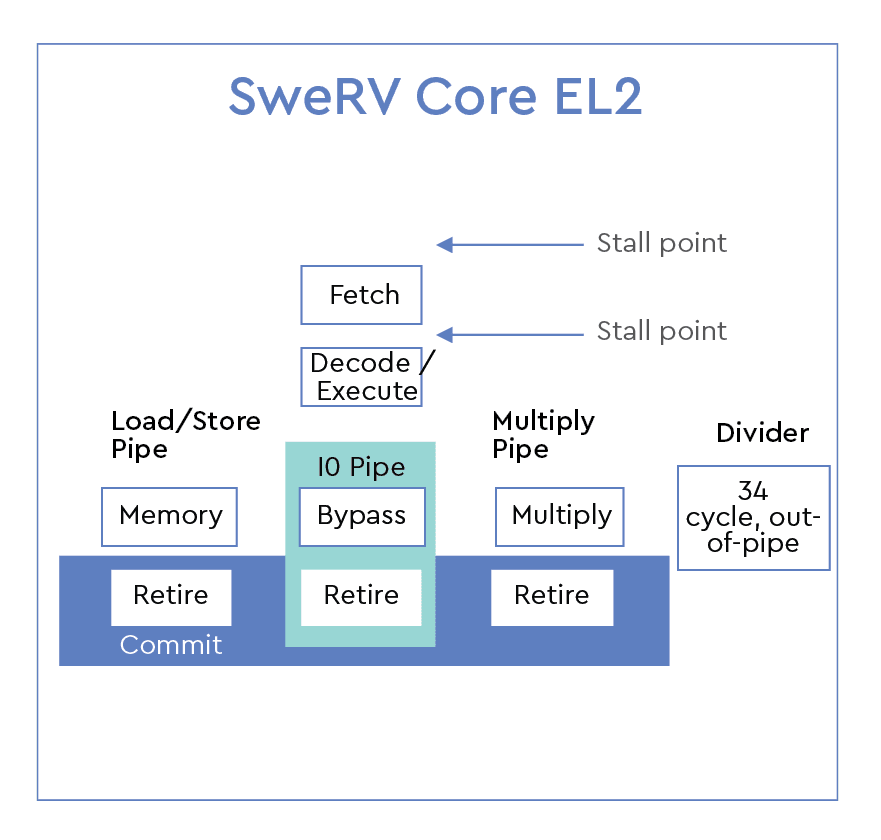

Western Digitalは3つのRISC-V Core、SweRV Core EH1、EH2、EL2を開発しました。

Core名

スレッド

CoreMarks/Mhz

SweRV Core EH1

シングル

4.9

SweRV Core EH2

デュアル

6.3

SweRV Core EL2

シングル

3.6

Western Digital SweRV Core EHX1は、32ビット、双方向スーパースカラー、9段パイプラインコアです。SweRV Core EH2はEH1から構築されましたが、パフォーマンスを向上させるためにデュアルスレッド機能を追加しています。SweRV Core EL2は、中程度のパフォーマンスを備えた小型のコアです。SoCのステートマシンやその他のロジック機能を置き換えることができます。

近い将来、SweRV CoreはさまざまなWestern Digital製品で使用される予定です。これら3つのコアはすべて、CHIPS Alliance githubでオープンソース化されています。CHIPS Allianceはオープンソースハードウェアとオープンソースソフトウェアの設計ツールを開発する組織です。この組織はRTL開発のコストを削減する、バリアフリーのコラボレーション環境です。SweRV Core EH1はhttps://github.com/chipsalliance/Cores-SweRVで入手できます

EH2はこちら:https://github.com/chipsalliance/Cores-SweRV-EH2

EL2はこちら:https://github.com/chipsalliance/Cores-SweRV-EL2

ビデオ

RISC-V SweRV Coreファミリーの概要

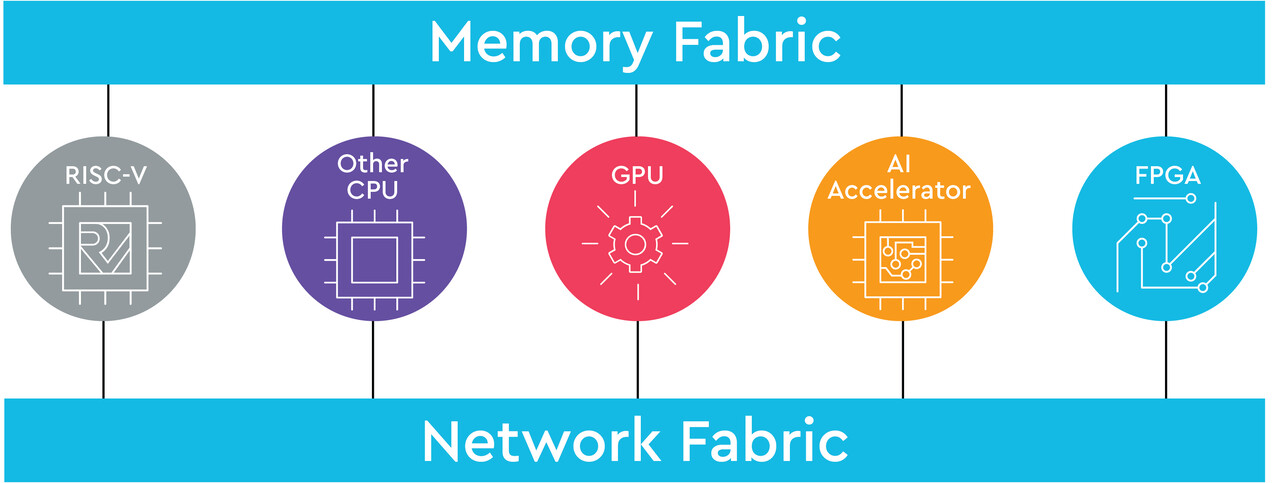

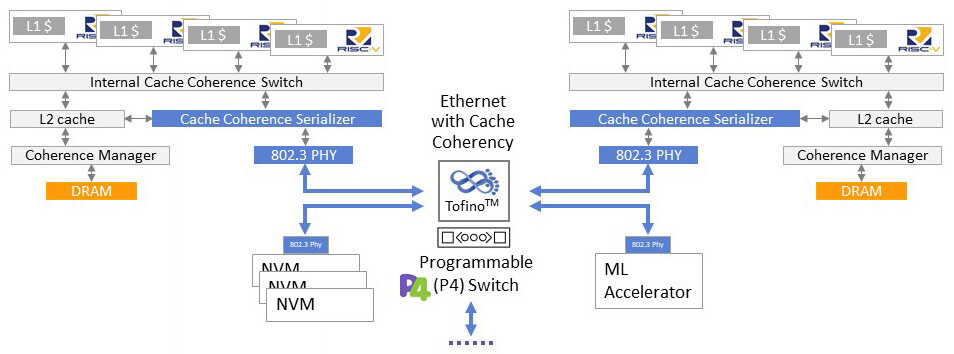

OmniXtend:コモディティファブリック上でキャッシュに直接アクセス

Western DigitalのOmniXtendは、最新のイーサネットスイッチのプログラマビリティを利用したオープンキャッシュコヒーレンスプロトコルであり、プロセッサのキャッシュ、メモリコントローラ、アクセラレータがイーサネット互換ファブリック上でコヒーレンスメッセージを直接交換できるようにします。永続性メモリーをプロセッサに効率的にアタッチするための完全にオープンなソリューションであり、コンピューター、ストレージ、メモリー、I/Oコンポーネントに接続する高度なファブリックが将来開発された場合、こうした技術をサポートする潜在能力があります。

OmniXtendはTileLinkコヒーレンスプロトコルに基づいて構築されており、プロセッサチップ外に拡張できます。OmniXtendデータプレーンのプログラマビリティにより、新しいシステムソフトウェアや新しいASICを導入しなくても、プロトコルの将来の改善を現場にすぐに展開できます。OmniXtendの今後の開発は、CHIPS Alliance組織で行われます。詳細についてはこちらをご覧ください:https://github.com/chipsalliance/omnixtend

ビデオ

戦略的イノベーション:Western DigitalのRISC-V

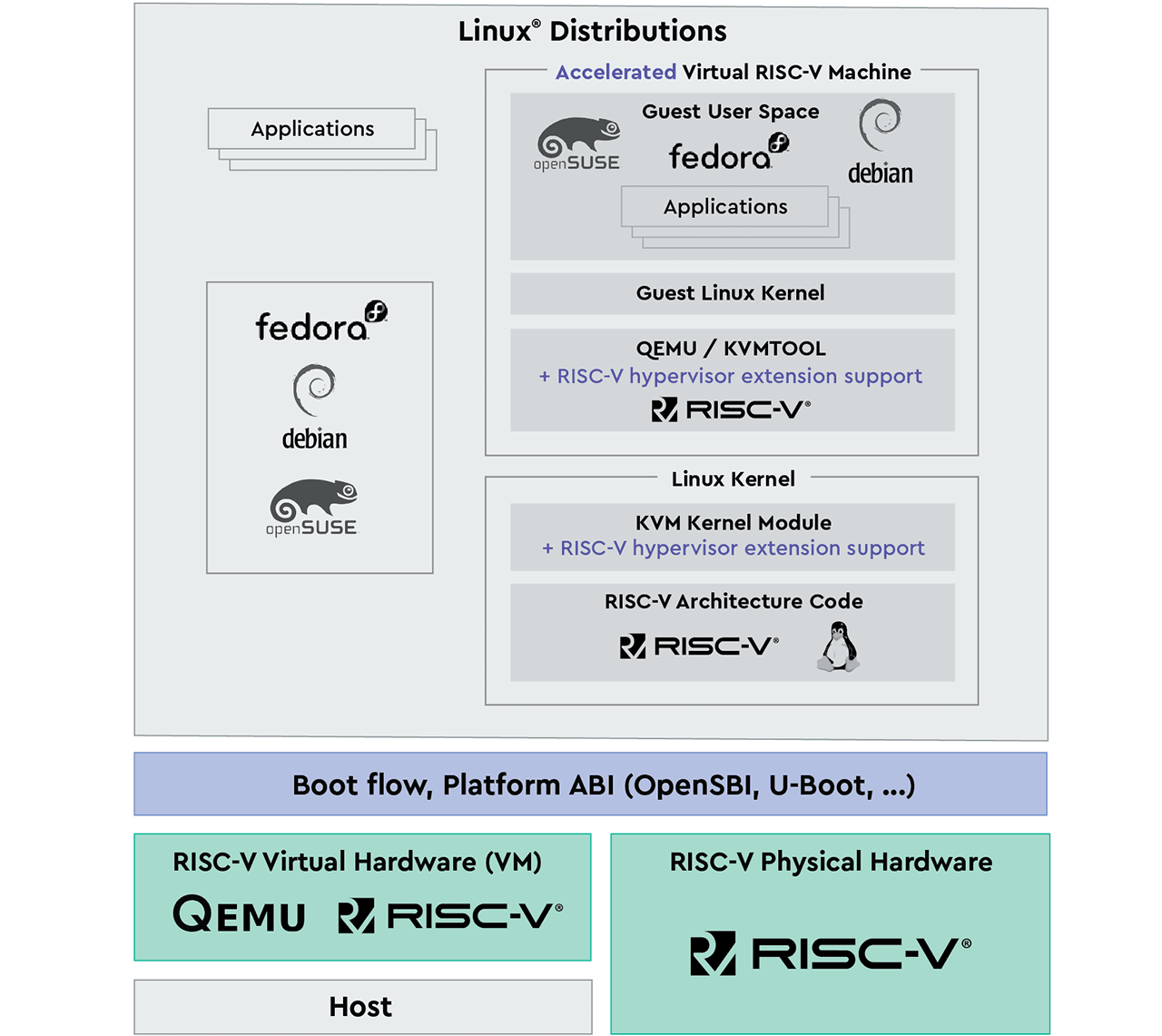

オープンソースRISC-Vソフトウェア

RISC-Vを活用させるには、それを取り巻く完全なソフトウェアエコシステムが必要です。エコシステムのコンポーネントは非常に多様であり、低レベルのファームウェアとブートローダーから完全に機能するオペレーティングシステムカーネルやアプリケーションに至るまで、すべてのレイヤーに広がっています。これらの各コンポーネントは、RISC-Vの成功に不可欠であり、オープンソースの普及の拡大により構築が促進されています。

Western Digitalはエコシステムのイノベーションを促進するために、Linuxコミュニティに大きく貢献しています。詳しくはhttps://github.com/kvm-riscvをご覧ください。

お勧めのダウンロード

情報へのアクセスがあれば、可能性は無限です。データの流れを加速してデータを強化しましょう。

データ集約型分野のイノベーション

ビデオ

RISC-V Summit 2019:Unshackling Memory!(解き放たれるメモリ)

2020年1月15日

Western Digital 2019 RISC-V Summitの基調講演で新しいSweRV CoreとOmniXtendのリファレンス設計を発表

ビデオ

RISC-V Summit 2019:

RISC-V and Chips Alliance Address new Compute Requirements(RISC-VおよびChips Allianceが新しいコンピューティング要件に対応)

2020年1月15日

2019 RISC-V SummitでのCHIPS Allianceの基調講演で、同組織と最新の開発への取り組みについて説明してます。

ビデオ

RISC-V Summit 2019:An Open and Coherent Memory Centric Architecture Enabled by RISC-V(RISC-Vによって実現したオープンでコヒーレントなメモリ中心のアーキテクチャ)

2020年1月15日

キャッシュコヒーレントイーサネットベースのメモリファブリックであるOmniXtendの技術アップデート。

ビデオ

RISC-V Summit 2019:SweRV Cores Roadmap(SweRV Coreロードマップ)

2020年1月15日

Western Digitalの新しいRISC-V SweRV Core EH2およびEL2の技術的詳細。

ビデオ

RISC-V Summit 2019:Headline Sponsor Western Digital presents GCC Compiler Code Size Density(最大のスポンサーであるWestern DigitalがGCCコンパイラのコードサイズ密度を発表)

2020年1月15日

RISC-Vの最新のGCCコード密度の改善。

ビデオ

RISC-V Summit 2019:Headline Sponsor Western Digital presents RISC V Hypervisor Support(最大のポンサーであるWestern DigitalがRISC Vハイパーバイザーサポートを発表)

2020年1月15日

RISC-VのQEMUおよびハイパーバイザーサポートに関する技術アップデート。

イベント

RISC-Vイベント

2019年4月4日

RISC-V Foundationは定期的にイベントやワークショップを開催しています。お近くのイベントにぜひご参加ください。

ビデオ

OmniXtend、オープンキャッシュコヒーレントメモリーファブリック

2019年1月12日

Western DigitalのOmniXtendを詳しく解説し、コモディティファブリック上でのキャッシュへの直接アクセスについて説明しています。このオープンキャッシュコヒーレンシバスにより、異種デバイスがメインメモリと同じようにアクセスできるようになります。

ビデオ

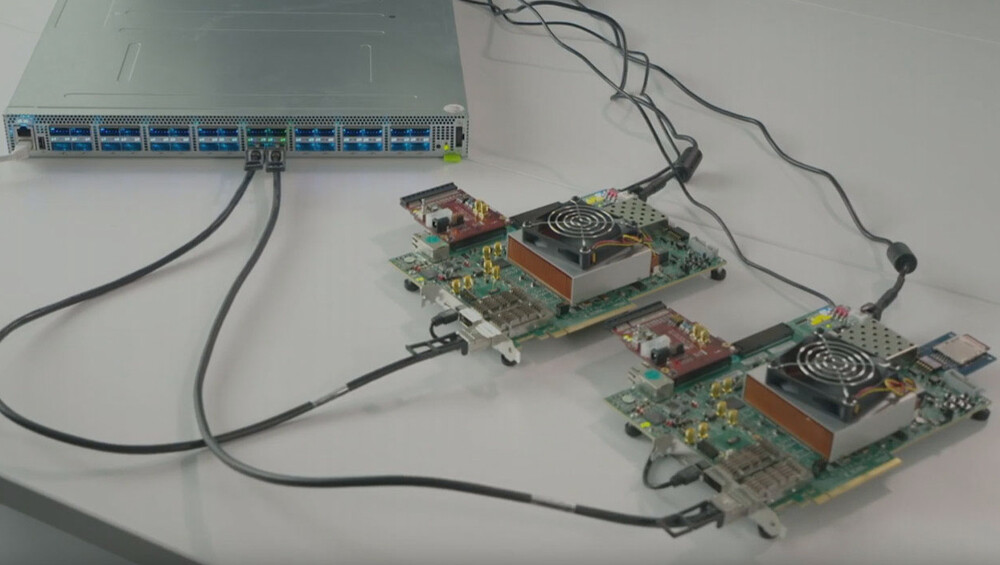

RISC-VとTofinoを使用してOmniXtendコヒーレントメモリーファブリックデモをセットアップする方法

2019年1月20日

OmniXtendのデモの設定方法を詳しく解説したビデオです。このデモでは2基のFPGAボードとプログラム可能なイーサネットスイッチを使用しています。FPGAボードのプログラミングと、スイッチでの実行に必要なP4コードについて説明しています。

ブログの特集記事

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

詳細を読むRISC-V

についてご興味がありましたら、

ぜひお問い合わせください。

開示情報

1. 社内テストに基づく