RISC-V:加速滿足

下一代

計算需求

發展 RISC-V 生態系統

RISC-V 屬於開放式 ISA,它將開啟處理器創新的紀元。為進一步加速開放標準介面和 RISC-V 處理架構,Western Digital 提供了硬體和軟體解決方案來協助發展 RISC-V 生態系統。

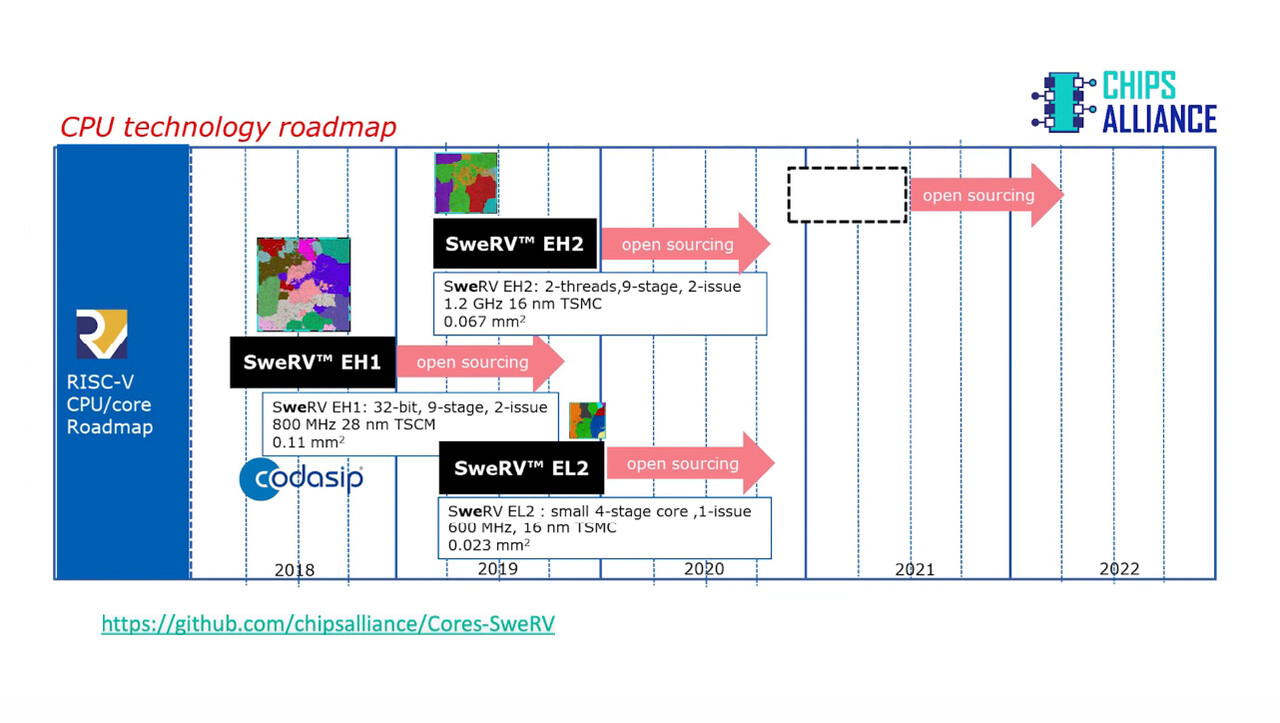

RISC-V SweRV CoreTM 系列

Western Digital 已開發三款 RISC-V 核心,分別是 SweRV Core EH1、EH2 和 EL2

核心名稱

執行緒

CoreMark/Mhz

SweRV Core EH1

單一

4.9

SweRV Core EH2

雙重

6.3

SweRV Core EL2

單一

3.6

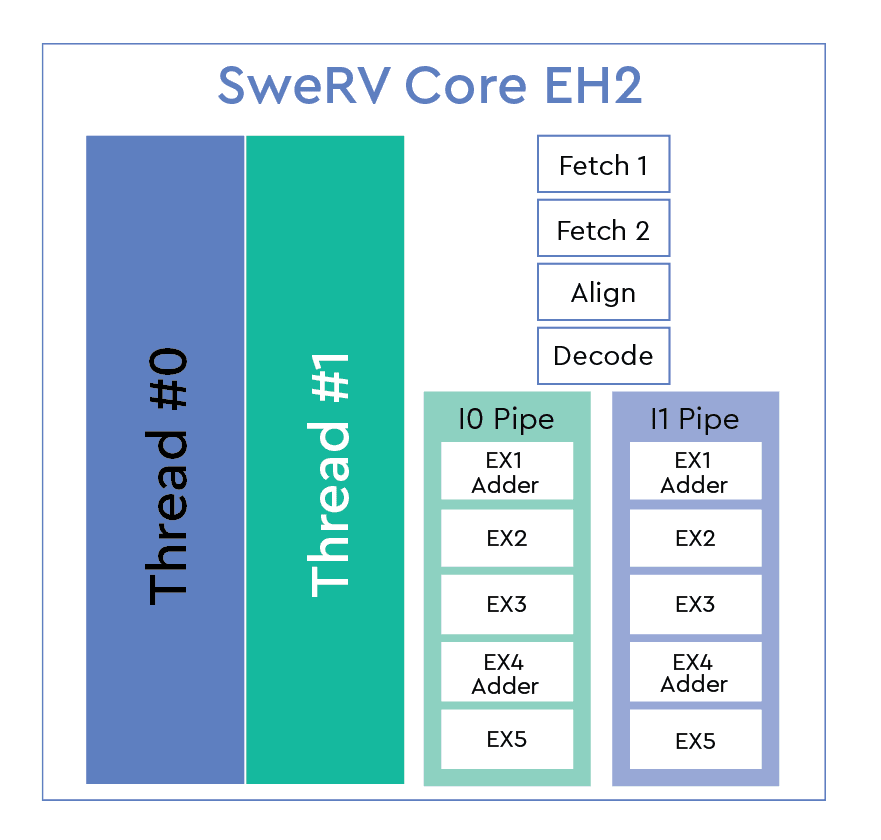

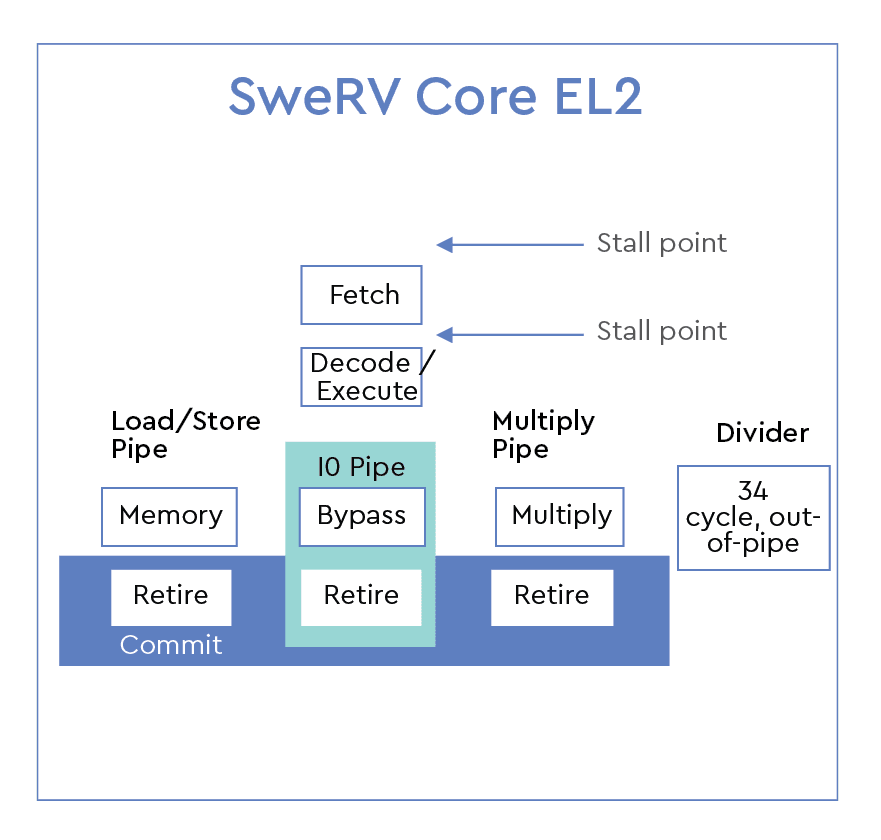

Western Digital SweRV Core EH1 是 32 位元雙路超標量結構的 9 級管線核心。基於 EH1 構建的 SweRV Core EH2 新增了雙重執行緒功能,可提升效能。最後,SweRV Core EL2 是中等效能的較小核心。其旨在取代 SoC 中的狀態機器和其他邏輯功能。

SweRV Core 會在近期用於多種 Western Digital 產品。所有三個核心在 CHIPS Alliance Github 中均為開放原始碼。CHIPS Alliance 是一家開發開放原始碼硬體與開放原始碼軟體設計工具的組織。它提供無障礙的協作環境,可降低 RTL 開發的成本。https://github.com/chipsalliance/Cores-SweRV 上提供 SweRV Core EH1

https://github.com/chipsalliance/Cores-SweRV-EH2 上提供 EH2。

https://github.com/chipsalliance/Cores-SweRV-EL2 上提供 EL2。

影片

RISC-V SweRV Core 系列概覽

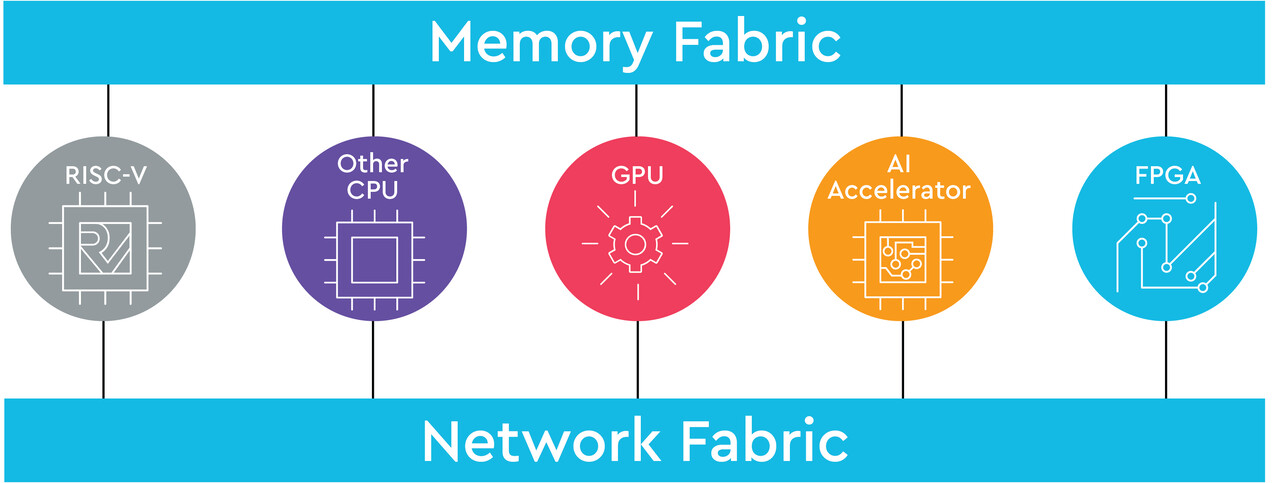

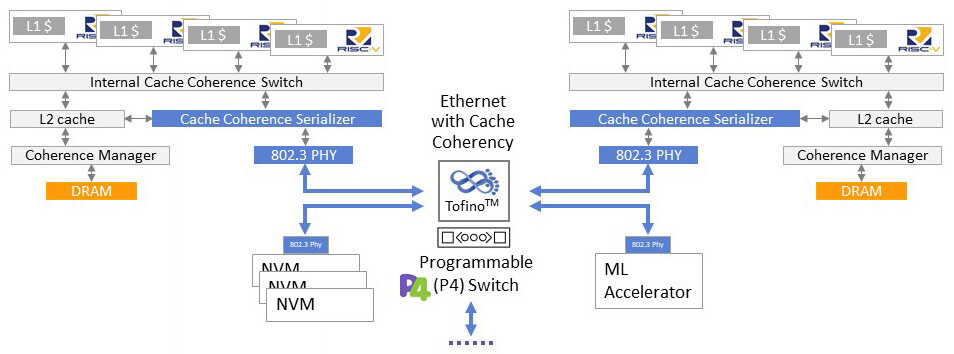

OmniXtend:透過商用架構直接快取

Western Digital 的 OmniXtend 是一種開放式快取同調協議,利用程式化設計的現代乙太網交換器實現處理器快取、記憶體控制器和加速器功能,直接透過與乙太網相容的架構交換同調訊息。這是真正的開放解決方案,可以有效地將持續內存與處理器連結,並為未來連接運算、存儲、內存和 I/O 組件時可能使用的進階結構提供支援。

基於 TileLink 同調協議的 OmniXtend 能夠提供超出處理器晶片的效能。OmniXtend 資料平面的程式化設計為將來對協議進行改進,並立即在現場部署奠定了基礎,並且完全無需任何新的系統軟體或新 ASIC。OmniXtend 未來的開發將在 CHIPS Alliance 組織內完成。如需更多資訊,請參閱 https://github.com/chipsalliance/omnixtend。

影片

策略創新:Western Digital 的 RISC-V

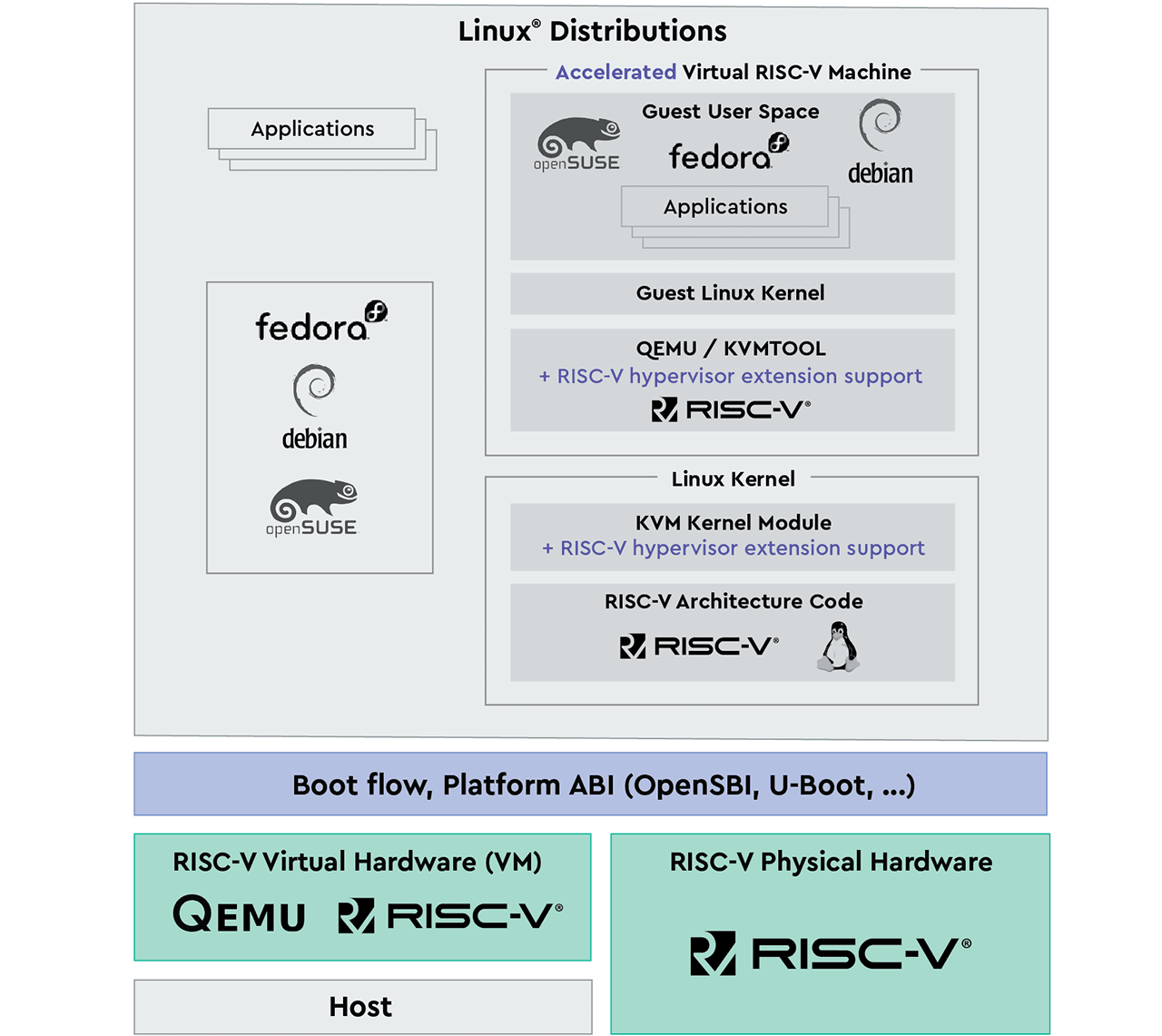

開放原始碼 RISC-V 軟體

為實現快速發展,RISC-V 需要在週邊構建一套完整的軟體生態系統。此生態系統的組成部分存在很高的多樣化要求,覆蓋下至從低層級韌體和開機載入器,上至全功能操作系統核心與應用程式的所有層級。其中每個組成部分對確保 RISC-V 的成功,以及透過開放原始碼的優勢來加速構建都有重要作用。

為鼓勵生態系統內的創新,Western Digital 在 Linux 社群中貢獻了許多內容。如需更多資訊,請造訪:https://github.com/kvm-riscv。

精選下載項目

當您能存取資訊時,便有了無限的可能。加快資料流動,推動資料蓬勃發展。

為以資料為中心的世界提供創新

影片

2019 年 RISC-V 高峰會:釋放記憶體!

2020 年 1 月 15 日

Western Digital 2019 年 RISC-V 高峰會專題演講中宣布推出全新 SweRV Core 和 OmniXtend 參考設計

影片

2019 年 RISC-V 高峰會:

RISC-V 和 Chips Alliance 滿足新的計算需求

2020 年 1 月 15 日

CHIPS Alliance 在 2019 年 RISC-V 高峰會上的專題演講,其中將介紹與組織及與開發工作相關的最新資訊。

影片

2019 年 RISC-V 高峰會:由 RISC-V 提供支援,以記憶體為中心的開源一致性架構

2020 年 1 月 15 日

關於 OmniXtend (基於快取一致性乙太網路的記憶體架構) 的技術更新。

影片

2019 年 RISC-V 高峰會:SweRV Core 藍圖

2020 年 1 月 15 日

關於 Western Digital 全新 RISC-V SweRV Core EH2 和 EL2 的技術詳細資料。

影片

2019 年 RISC-V 高峰會:冠名贊助商 Western Digital 展示 GCC 編譯器代碼大小密度

2020 年 1 月 15 日

針對 RISC-V 的最新 GCC 代碼密度改善。

影片

2019 年 RISC-V 高峰會:冠名贊助商 Western Digital 展示 RISC V Hypervisor 支援

2020 年 1 月 15 日

關於 QEMU 的技術更新及針對 RISC-V 的 Hypervisor 支援。

活動

RISC-V 活動

2019 年 4 月 4 日

RISC-V 基金會定期舉辦活動和研討會。參加您附近的活動。

影片

OmniXtend,開源快取一致性記憶體架構

2019 年 6 月 12 日

Western Digital 的 OmniXtend 概覽。透過商用架構直接快取。利用此開放原始碼快取同調匯流排,異構裝置現在可以公平地存取主要記憶體。

影片

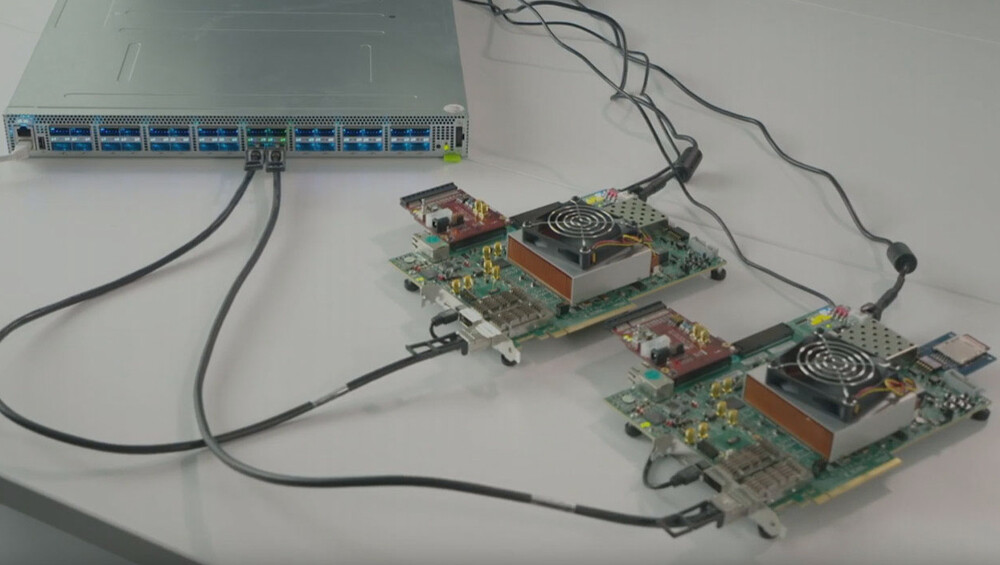

示範:如何使用 RISC-V 和 Tofino 設定 OmniXtend 一致性記憶體架構

2019 年 6 月 20 日

詳細介紹如何設置 OmniXtend 示範的影片。此示範中使用兩塊 FPGA 板和一個程式化設計的乙太網交換器。其中說明了 FPGA 板的程式和需要在交換器上執行的 P4 代碼。

我們部落格上的精選文章

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

閱讀更多內容您是否對

RISC-V 感興趣?

聯繫我們。

公開事項

1. 依據內部測試