-

Solutions

For personal storage solutions visit these Western Digital brands

BUCKLE UP

Counterpoint Research estimated the storage capacity requirement for autonomous vehicles to balloon over 2TB in the next decade

-

Innovations

ZONED STORAGE

Addresses data center scale with increased capacity, better QoS with lower TCO

RISC-V: Accelerating

Next-Generation

Compute Requirements

Gartner's Report on RISC-V momentum in IoT and business environments

GARTNER is a registered trademark and service mark of Gartner, Inc. and/or its affiliates in the U.S. and internationally and is used herein with permission. All rights reserved.

Attributions for Gartner Research Documents:

Gartner, Market Trends: Custom ICs Based on RISC-V Will Enable Cost-Effective IoT Product

Differentiation, Amy Teng, 5 June 2020

Growing the RISC-V Ecosystem

RISC-V is an open ISA enabling a new era of processor innovation. To further accelerate open standard interfaces and RISC-V processing architectures, Western Digital has contributed hardware and software solutions to help grow the RISC-V ecosystem.

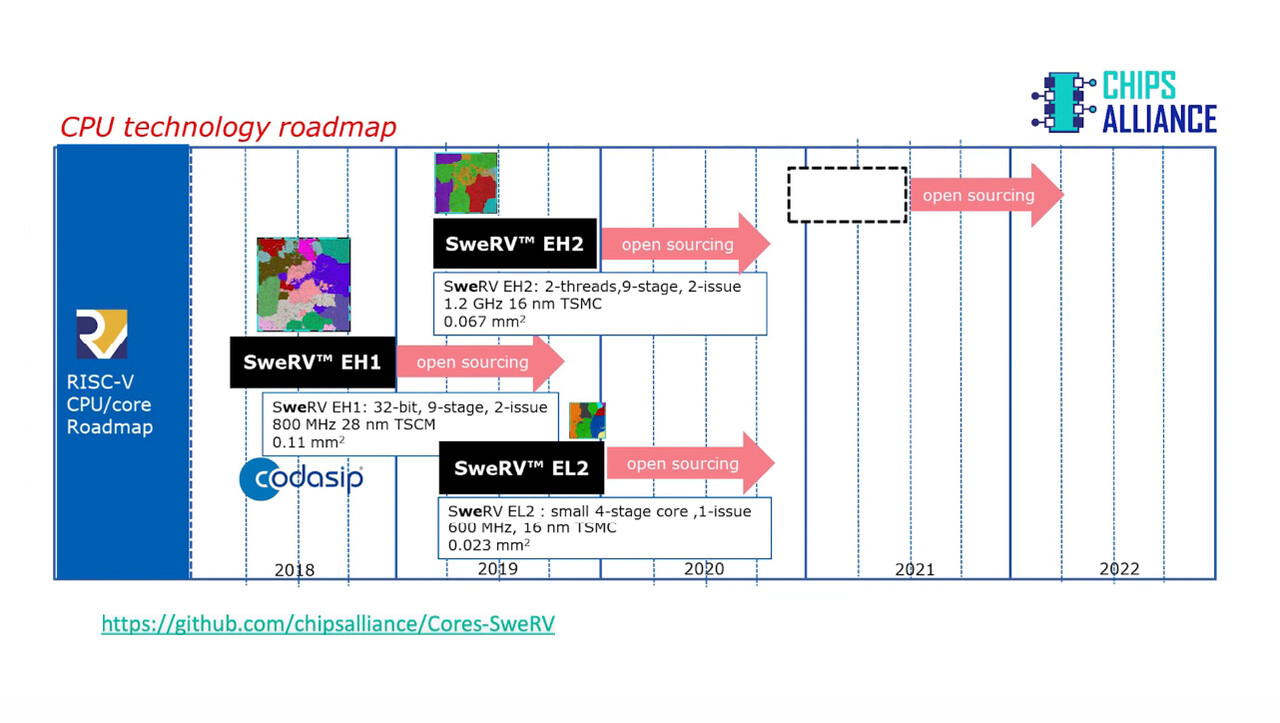

The RISC-V SweRV CoreTM Family

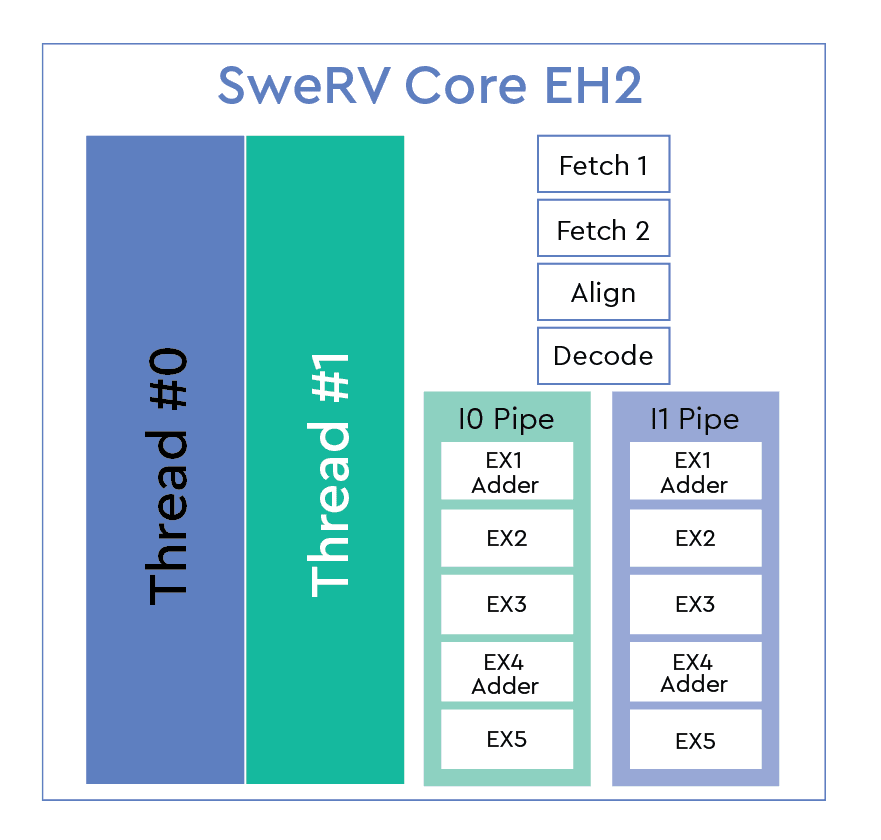

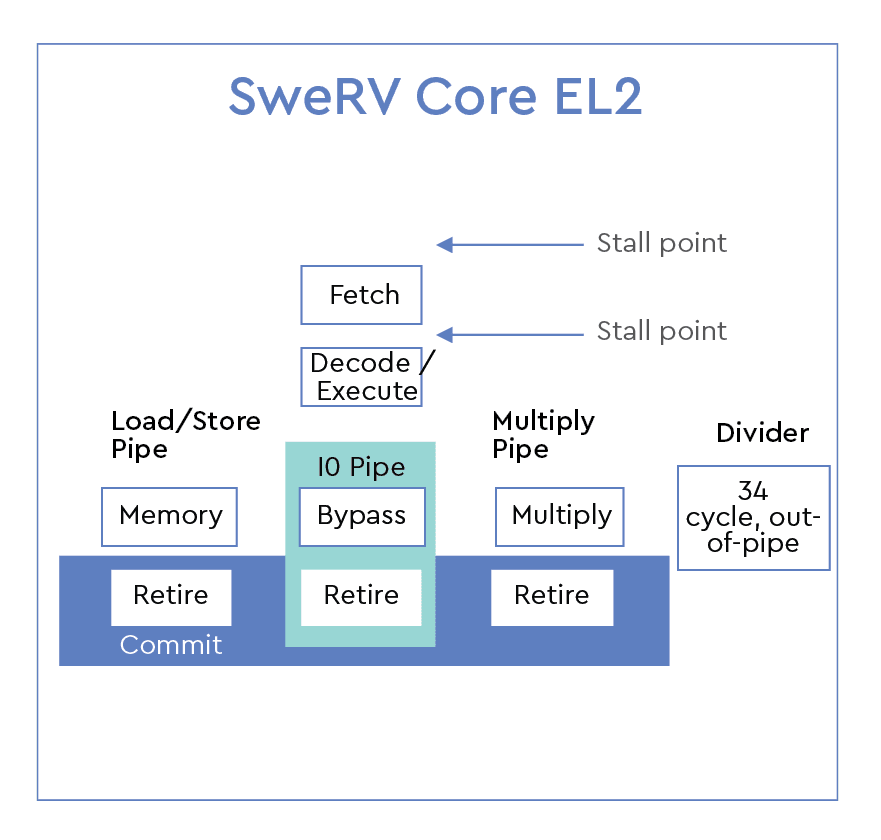

Western Digital has developed three RISC-V Cores, the SweRV Core EH1, EH2 and EL2.

Core Name

Threads

CoreMarks/Mhz

SweRV Core EH1

Single

5.7

SweRV Core EH2

Single

6

SweRV Core EH2

Dual

7.8

SweRV Core EL2

Single

4.3

The Western Digital SweRV Core EH1 is a 32-bit, 2-way superscalar, 9 stage pipeline core. The SweRV Core EH2 was built off of the EH1, but adds dual threaded capability for additional performance. Lastly the SweRV Core EL2 is a smaller core with moderate performance. It was designed to replace state machines and other logic functions in SoCs.

The SweRV Cores will be used in a variety of Western Digital products in the near future. All three cores have been open sourced in CHIPS Alliance github. CHIPS Alliance is an organization that develops open source hardware and open source software design tools. It is a barrier free, collaborative environment which lowers the cost of RTL development. The SweRV Core EH1 is available at https://github.com/chipsalliance/Cores-SweRV

The EH2 is here, https://github.com/chipsalliance/Cores-SweRV-EH2

And the EL2 is here, https://github.com/chipsalliance/Cores-SweRV-EL2

Video

RISC-V SweRV Core Family Overview

OmniXtend: Direct to Caches over Commodity Fabric

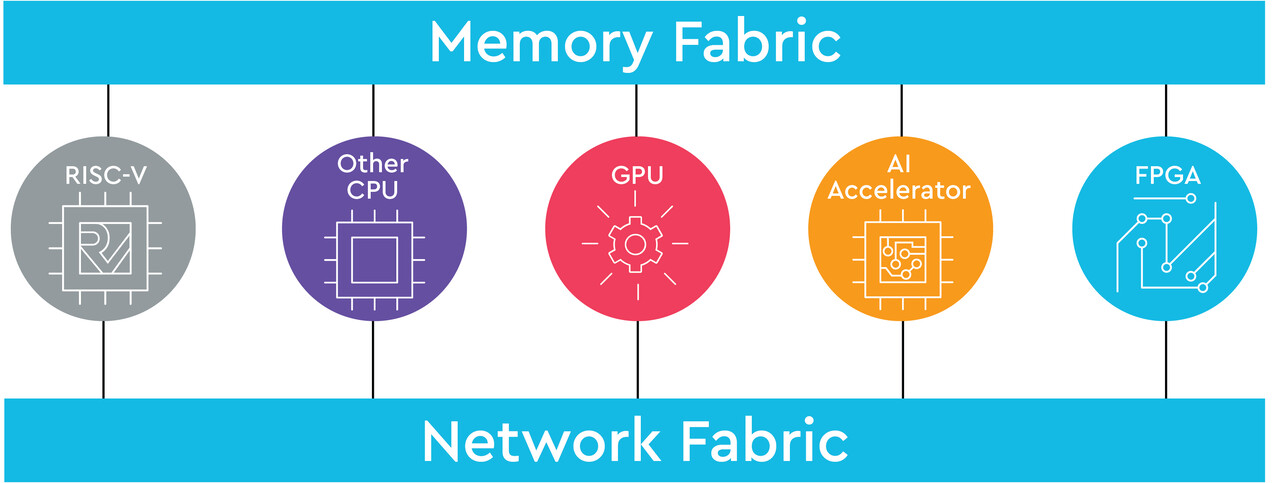

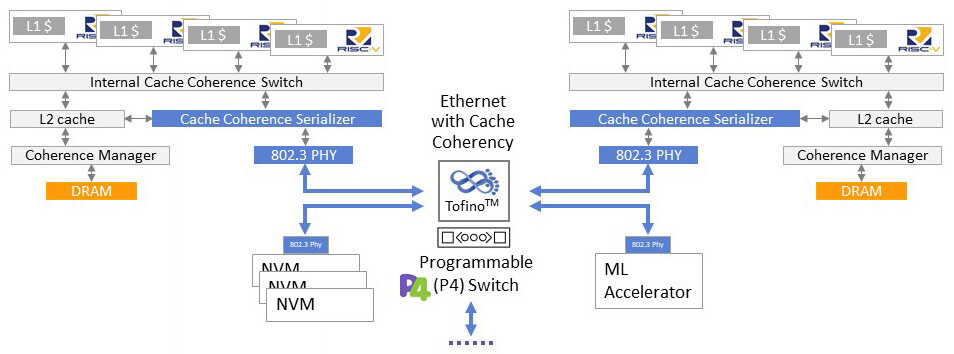

Western Digital’s OmniXtend is an open cache coherence protocol utilizing the programmability of modern Ethernet switches to enable processors’ caches, memory controllers and accelerators to exchange coherence messages directly over an Ethernet-compatible fabric. It is a truly open solution for efficiently attaching persistent memory to processors and offers potential support of future advanced fabrics that connect compute, storage, memory and I/O components.

OmniXtend builds upon the TileLink coherence protocol, to scale beyond the processor chip. The programmability of OmniXtend dataplane allows future improvements to the protocol to be deployed immediately in the field, without requiring new system software or new ASICs. Further developments of OmniXtend will be done in the CHIPS Alliance organization. Further details can be found at https://github.com/chipsalliance/omnixtend.

Video

Strategic Innovation: RISC-V at Western Digital

Open Source RISC-V Software

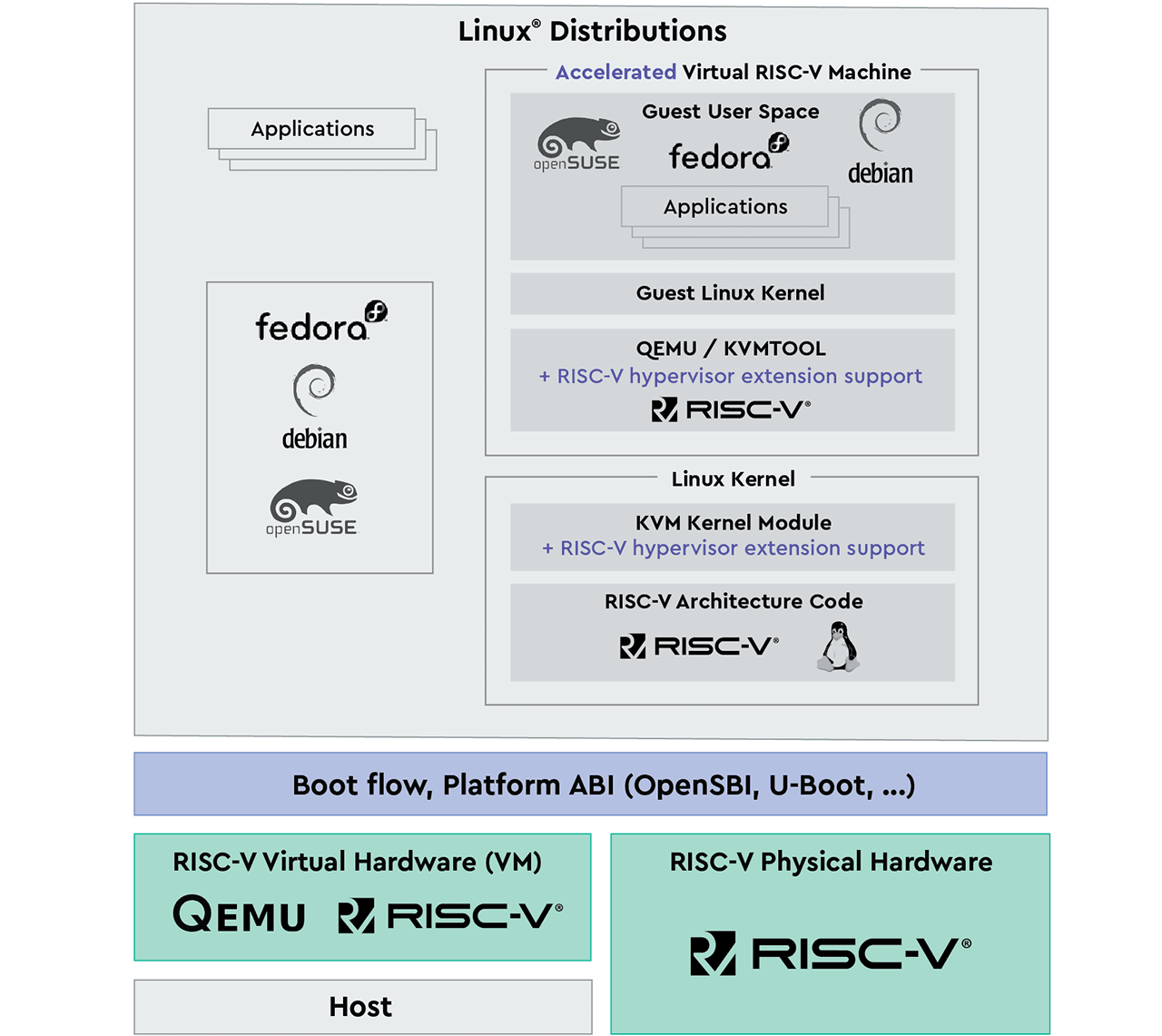

RISC-V needs a complete software ecosystem surrounding it in order to thrive. The components of the ecosystem are very diverse, spreading across all layers from low level firmware and boot loaders up to a fully functional operating system kernel and applications. Each of these components is important to ensure the success of RISC-V and the power of open source contributions accelerates the build out.

To help encourage innovation in the ecosystem, Western Digital has made numerous contributions to the Linux community. Further details are available at https://github.com/kvm-riscv.

Featured Downloads

When you have access to information, the possibilities are endless. Accelerate the flow of your data, so your data can thrive.

Innovating for a Data-Centric World

Video

RISC-V 2020 Summit: The March of RISC-V

Dec 8, 2020

Western Digital 2020 RISC-V Summit Keynote discussing next generation storage and compute. Siva Sivaram discusses Western Digital’s first RISC-V SweRV Core SoC in a prototype SSD. Updates to the SweRV Core family and an invitation to collaborate on a unified memory standard for heterogeneous processing.

Video

RISC-V Summit 2020:

Omnixtend Boot Protocol and Coherent Scaleout - Dejan Vucinic, Western Digital Corporation

SEP 3, 2020

Over the past eighteen months OmniXtend has become the de facto standard for building multi-socket RISC-V systems. Recent efforts within the Interconnects Workgroup in CHIPS Alliance resulted in the definition of an initialization and configuration protocol which enables the construction of massively parallel systems of arbitrary size. This is a simple yet race-free approach to setting up any number of coherent endpoints at boot. It enables different system models: a single instance of an operating system over several nodes with Non-Uniform Memory Access (NUMA) or independent instances of operating systems on different nodes sharing global memory coherently and peripherals non-coherently. This talk will cover the basics of the protocol and the currently enabled usage scenarios, as well as the future vision for fault-tolerance and coherent hotplug.

Video

RISC-V Summit 2020: Where Is the 32-Bit Glibc Port? - Alistair Francis, Western Digital

SEP 3, 2020

The process to upstream 32-bit RISC-V (RV32) has been going on for over two years now. This talk will cover why the process has taken so long, what is upstream and what still remains to be done.

This will hopefully be the first upstream architecture that is 32-bit but has a 64-bit time_t. This means that the architecture is y2038 safe and only works on the Linux kernel 5.4+.

This talk will cover the Y2038 Unix Epoch overflow problem and what is being done to fix it. It will describe how and why this applies to the 32-bit RISC-V glibc port.

Video

RISC-V Summit 2020: The Open Source Hardware Roadmap - Zvonimir Bandic, Chairman, CHIPS Alliance

SEP 3, 2020

The RISC-V open ISA has enabled a new generation of processing architectures. There now exists an open hardware group, CHIPS Alliance where organizations, non-profits, individuals, and academia can collaborate to solve the next generation of processing challenges. See the milestones that CHIPS Alliance has already accomplished and learn about our roadmap and future vision for open source hardware.

Video

RISC-V Summit 2019:

RISC-V and Chips Alliance Address new Compute Requirements

Jan 15, 2020

CHIPS Alliance keynote at the 2019 RISC-V Summit explaining the organization and the latest development efforts.

Video

RISC-V Summit 2019: An Open and Coherent Memory Centric Architecture Enabled by RISC-V

Jan 15, 2020

Technical update on OmniXtend, a cache coherent Ethernet based memory fabric.

Video

RISC-V Summit 2019: SweRV Cores Roadmap

Jan 15, 2020

Technical details on Western Digital’s new RISC-V SweRV Core EH2 and EL2.

Video

RISC-V Summit 2019: Headline Sponsor Western Digital presents GCC Compiler Code Size Density

Jan 15, 2020

The latest GCC code density improvements for RISC-V.

Video

RISC-V Summit 2019: Headline Sponsor Western Digital presents RISC V Hypervisor Support

Jan 15, 2020

Technical update on QEMU and hypervisor support for RISC-V.

Event

RISC-V Events

Apr 4, 2019

The RISC-V Foundation regularly conducts events and workshops. Participate in an event near you.

Video

OmniXtend, an Open Cache Coherent Memory Fabric

Jun 12, 2019

A high level overview on Western Digital’s OmniXtend. A direct to caches over commodity Ethernet fabric. With this open cache coherency bus, heterogeneous devices can now access main memory equally.

Video

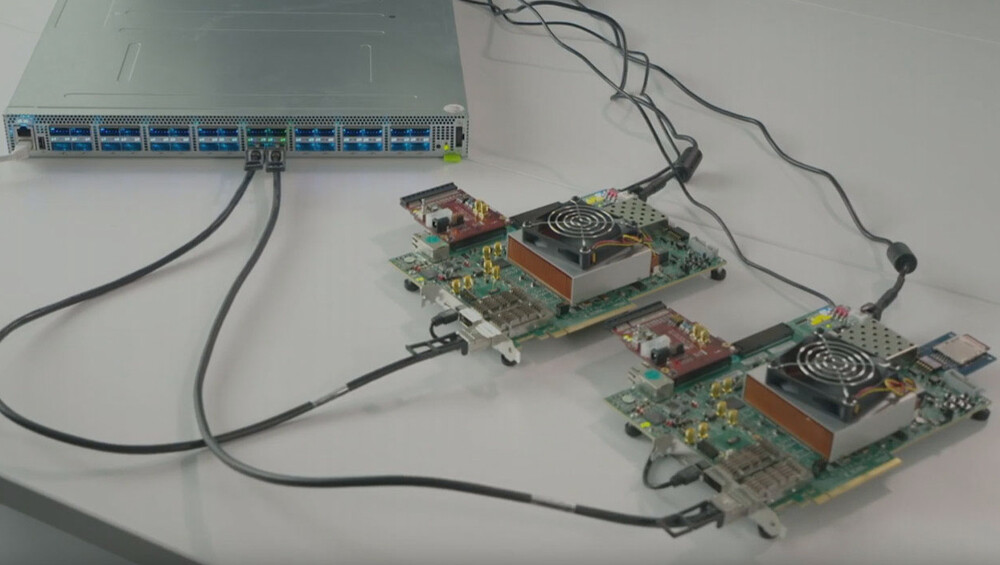

How to set up OmniXtend coherent memory fabric demo with RISC-V and Tofino

Jun 20, 2019

A detailed video explaining how to set up an OmniXtend demo. This demo uses two FPGA boards and a programmable Ethernet switch. It explains the programming of the FPGA boards and the P4 code needed to run on the switch.

Featured Articles from Our Blog

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

Read MoreInterested in

RISC-V?

Let’s connect.

Disclosures

1. Based on Internal Testing