-

Soluciones

Industrias

Casos de uso

Para ver soluciones de almacenamiento personal visite estas marcas de Western Digital

ABROCHEN SUS CINTURONES

ABROCHEN SUS CINTURONESUna investigación de Counterpoint Research ha estimado que la capacidad de almacenamiento requerida para vehículos autónomos en la próxima década puede escalar hasta los 2TB.

-

Innovaciones

Se posibilita una nueva era de arquitecturas de computación centradas en datos abiertos.

ZONED STORAGE

Aborda escala de centro de datos con más capacidad, mejor calidad de servicio con menor costo total de propiedad (TCO)

RISC-V: Aceleramos los

requisitos informáticos

de última generación

Crecimiento del ecosistema de RISC-V

RISC-V es una arquitectura de conjunto de instrucciones abierta que permite una nueva era de innovación en procesadores. Para acelerar aún más las interfaces estándar abiertas y las arquitecturas de procesamiento de RISC-V, Western Digital proporciona soluciones de hardware y software para ayudar en el crecimiento del ecosistema de RISC-V.

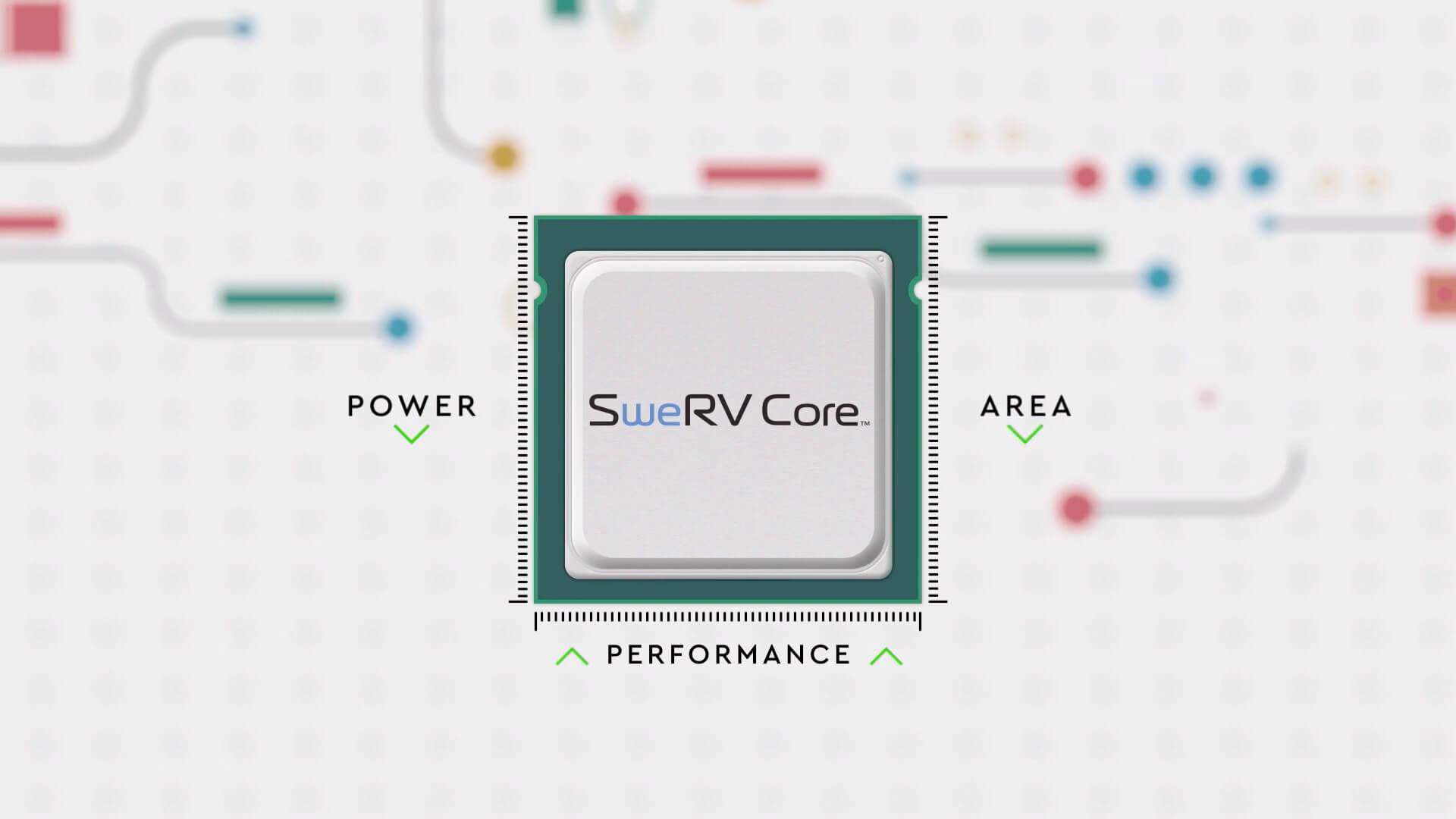

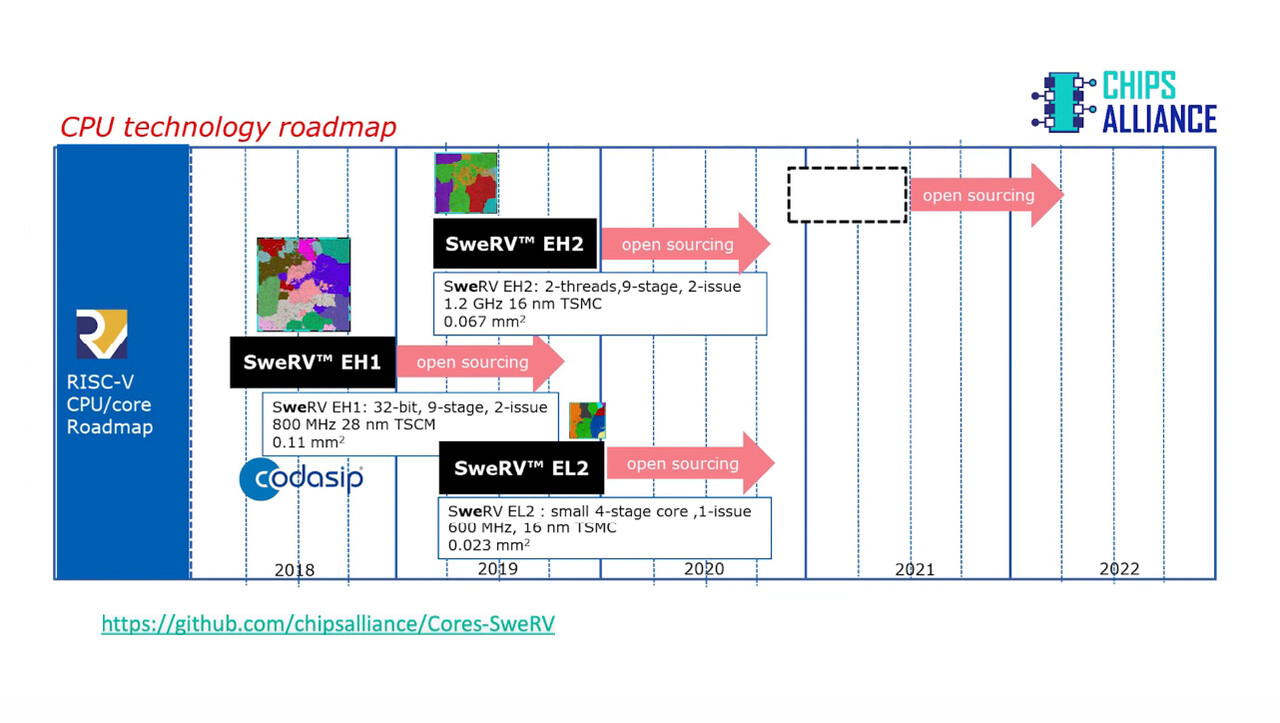

La familia RISC-V SweRV CoreTM

Western Digital desarrolló tres núcleos RISC-V: el SweRV Core EH1, EH2 y EL2.

Nombre del núcleo

Subprocesos

CoreMarks/Mhz

SweRV Core EH1

Simple

4,9

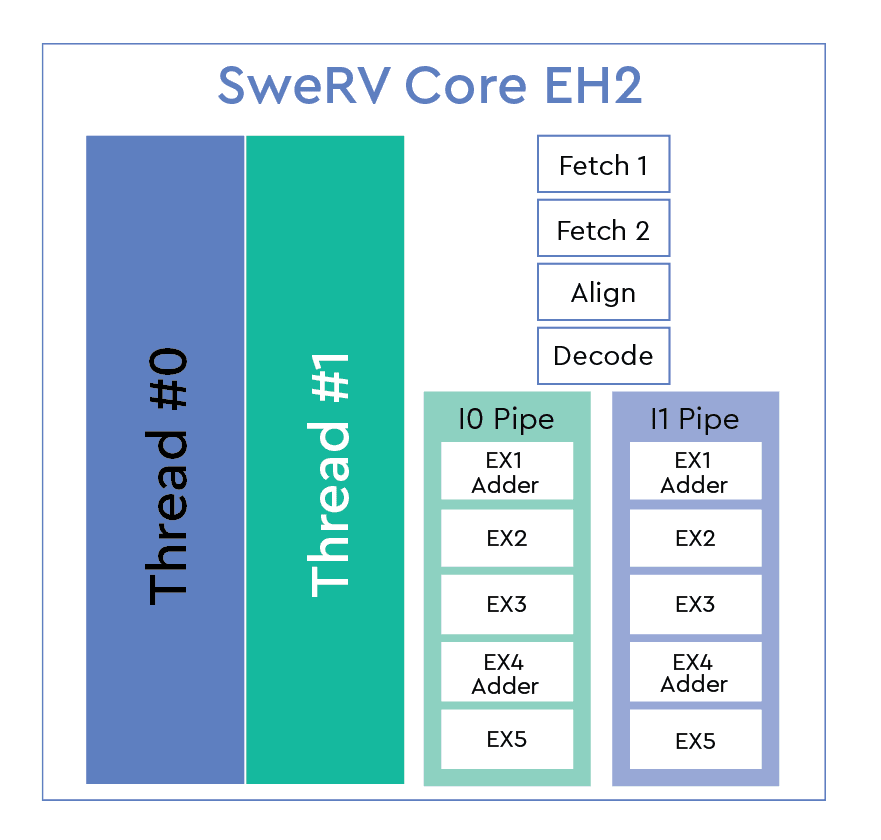

SweRV Core EH2

Doble

6,3

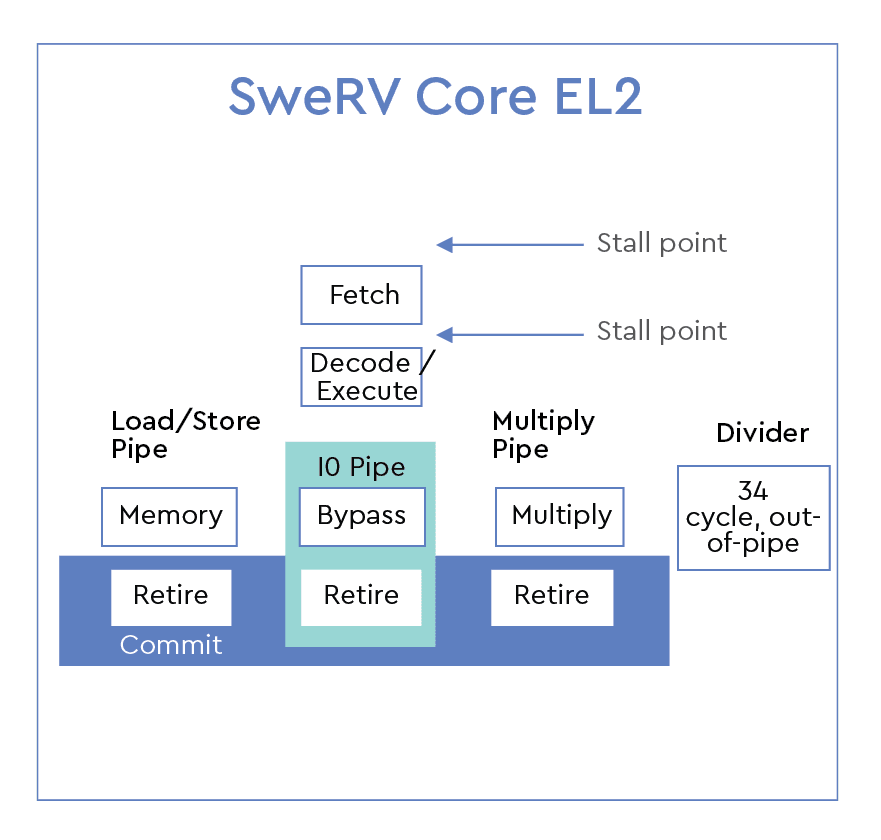

SweRV Core EL2

Simple

3,6

SweRV Core EH1 de Western Digital es un núcleo de sistema de 32 bits, escalamiento bidireccional y nueve etapas. SweRV Core EH2 se creó a partir del EH1, pero cuenta con una capacidad de subprocesos dobles para un rendimiento adicional. Por último, SweRV Core EL2 es un núcleo más pequeño con un rendimiento moderado. Se diseñó para reemplazar las máquinas de estados y otras funciones lógicas en sistemas en chip.

Los núcleos SweRV se utilizarán próximamente en una amplia variedad de productos de Western Digital. Los tres núcleos son de código abierto en la plataforma GitHub de CHIPS Alliance. CHIPS Alliance es una organización que desarrolla hardware de código abierto y herramientas de diseño de software de código abierto. Se trata de un entorno de colaboración sin obstáculos que reduce el costo del desarrollo del nivel de transferencia de registro (Register-Transfer Level, RTL). El núcleo SweRV EH1 está disponible en https://github.com/chipsalliance/Cores-SweRV

El EH2 está aquí https://github.com/chipsalliance/Cores-SweRV-EH2

Y el EL2 está aquí https://github.com/chipsalliance/Cores-SweRV-EL2

Video

Descripción general de la familia RISC-V SweRV Core

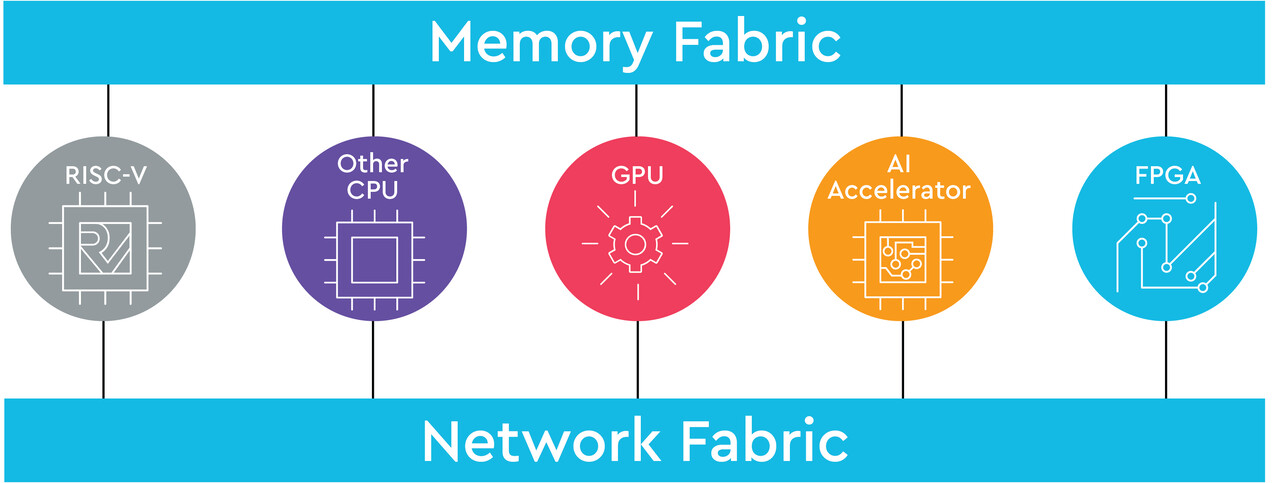

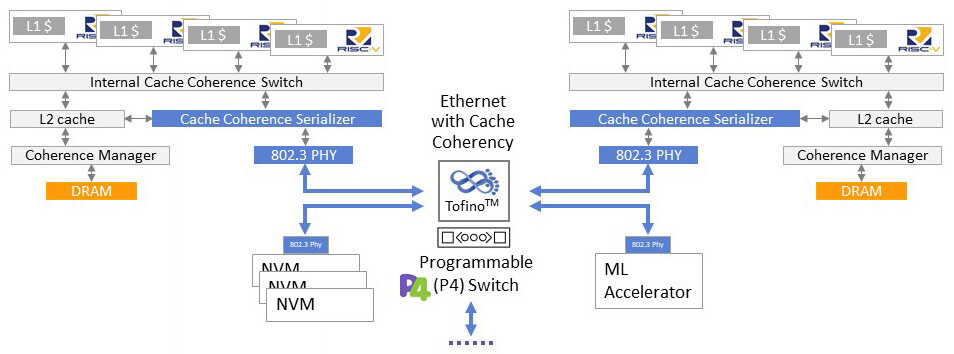

OmniXtend: Directo a las memorias caché por medio de la estructura básica

OmniXtend de Western Digital es un protocolo de coherencia de memoria caché abierta que utiliza la programabilidad de los interruptores Ethernet modernos para permitir que la memoria caché de los procesadores, los aceleradores y los controladores de memoria puedan intercambiar mensajes coherentes directamente desde una estructura compatible con Ethernet. Es una solución realmente abierta para adjuntar de forma eficiente la memoria persistente a los procesadores y ofrece compatibilidad potencial para estructuras avanzadas futuras que conecten componentes de informática, almacenamiento, memoria y E/S.

OmniXtend se basa en el protocolo de coherencia de TileLink para escalar por encima de un microprocesador. La programabilidad del plano de datos de OmniXtend permite mejoras futuras en el protocolo para que pueda implementarse de inmediato en el campo, sin necesidad de un software de sistema nuevo ni circuitos integrados de aplicación específica. Se realizarán desarrollos adicionales de OmniXtend en la organización CHIPS Alliance. Para ver más detalles, consulte https://github.com/chipsalliance/omnixtend.

Video

Innovación estratégica: RISC-V en Western Digital

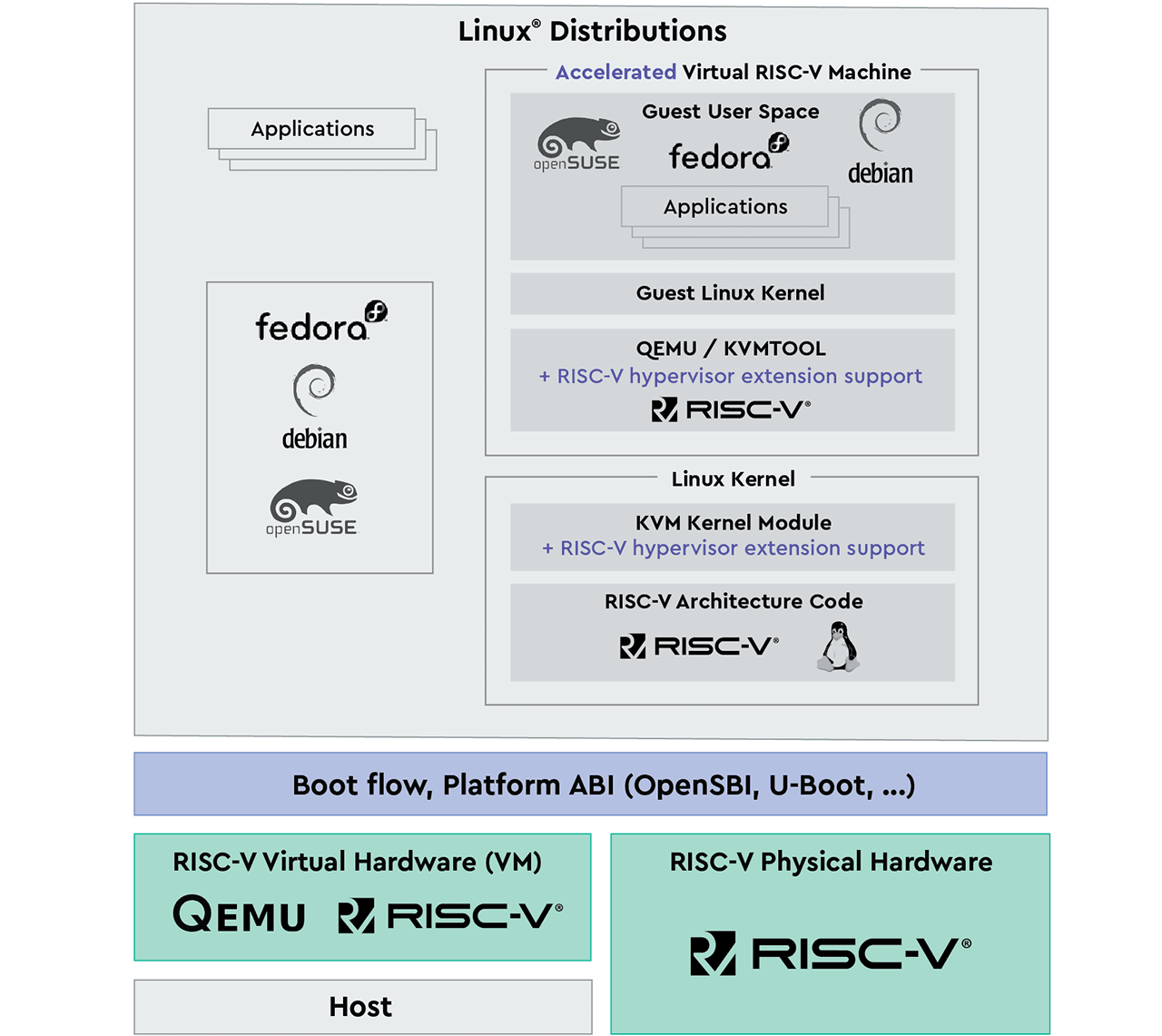

Software de RISC-V de código abierto

RISC-V necesita rodearse de un ecosistema de software completo para evolucionar. Los componentes del ecosistema son muy diversos; se extienden por todas las capas, desde el firmware de bajo nivel y los cargadores de arranque hasta un núcleo de sistema operativo y aplicaciones totalmente funcionales. Cada uno de estos componentes es fundamental para asegurar el éxito de RISC-V. Además, la potencia de las contribuciones de código abierto acelera ese éxito.

Con el fin de ayudar a fomentar la innovación en el ecosistema, Western Digital ha realizado numerosas contribuciones a la comunidad Linux. Si desea obtener más información, visite https://github.com/kvm-riscv.

Descargas destacadas

No hay límites cuando tiene acceso a la información. Acelere el flujo de sus datos, para que estos puedan prosperar.

Innovación para el mundo que gira alrededor de los datos

Video

Cumbre 2019 de RISC-V: ¡Memoria inquebrantable!

15 de enero de 2020

Presentación de Western Digital en la Cumbre 2019 de RISC-V en la que se anuncian los nuevos SweRV Core y el diseño de referencia OmniXtend.

Video

Cumbre 2019 de RISC-V:

RISC-V y Chips Alliance abordan los nuevos requisitos informáticos

15 de enero de 2020

Presentación de CHIPS Alliance en la Cumbre 2019 de RISC-V en la que se explican la organización y los últimos esfuerzos de desarrollo.

Video

Cumbre 2019 de RISC-V: RISC-V permite una arquitectura abierta y consistente centrada en la memoria

15 de enero de 2020

Actualización técnica de OmniXtend, una estructura de memoria caché consistente basada en Ethernet.

Video

Cumbre 2019 de RISC-V: Guía básica de los núcleos SweRV

15 de enero de 2020

Detalles técnicos acerca de los nuevos RISC-V SweRV Core EH2 y EL2 de Western Digital.

Video

Cumbre 2019 de RISC-V: El patrocinador principal Western Digital presenta el compilador GCC: densidad del tamaño del código

15 de enero de 2020

Las últimas mejoras en la densidad del código GCC para RISC-V.

Video

Cumbre 2019 de RISC-V: El patrocinador principal Western Digital presenta el soporte de hipervisor de RISC-V

15 de enero de 2020

Actualización técnica acerca de QEMU y el soporte de hipervisor para RISC-V.

Evento

Eventos RISC-V

4 de abril de 2019

La Fundación RISC-V suele llevar a cabo eventos y talleres. Participe del evento más cercano a usted.

Video

OmniXtend, una estructura de memoria caché consistente y abierta

12 de junio de 2019

Una descripción general de alto nivel sobre OmniXtend de Western Digital. Directo a las memorias caché por medio de la estructura básica Gracias a este bus de consistencia de la memoria caché abierta, los dispositivos heterogéneos ahora podrán acceder a la memoria principal de la misma forma.

Video

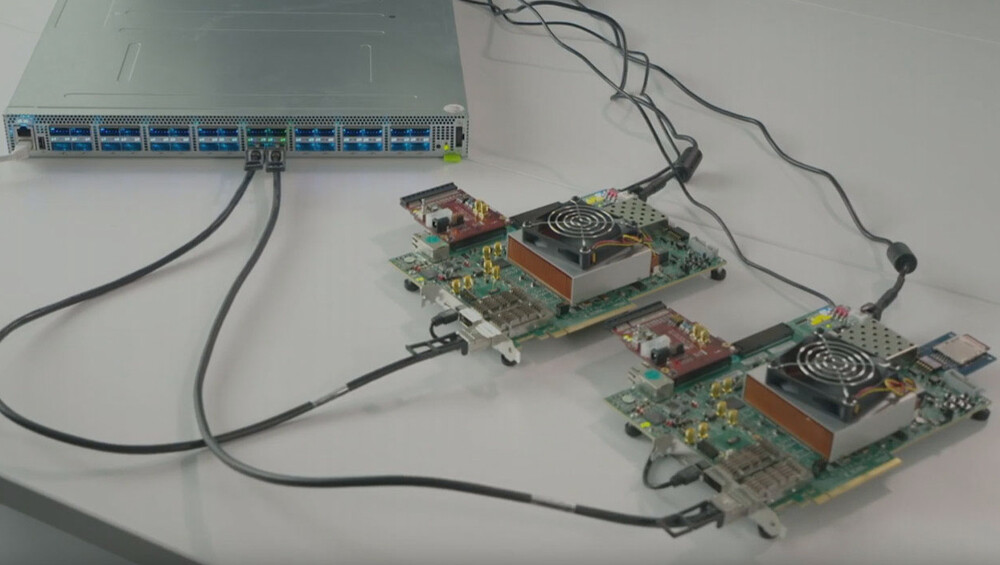

Cómo configurar la demostración de la estructura de memoria consistente OmniXtend con RISC-V y Tofino

20 de junio de 2019

Un video detallado que explica cómo configurar una demostración de OmniXtend. Esta demostración utiliza dos placas FPGA y un interruptor Ethernet programable. Además, explica la programación de las placas FPGA y el código P4 que se necesita para utilizar el interruptor.

Artículos destacados de nuestro blog

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

Leer más¿Está interesado en

RISC-V?

Conectémonos.

Divulgaciones

1. Basado en pruebas internas