RISC-V:加速满足

下一代

计算需求

发展 RISC-V 生态系统

RISC-V 是一个开启处理器创新新时代的开源 ISA。为进一步加速开放标准接口和 RISC-V 处理架构,Western Digital 提供了硬件和软件解决方案,帮助发展 RISC-V 生态系统。

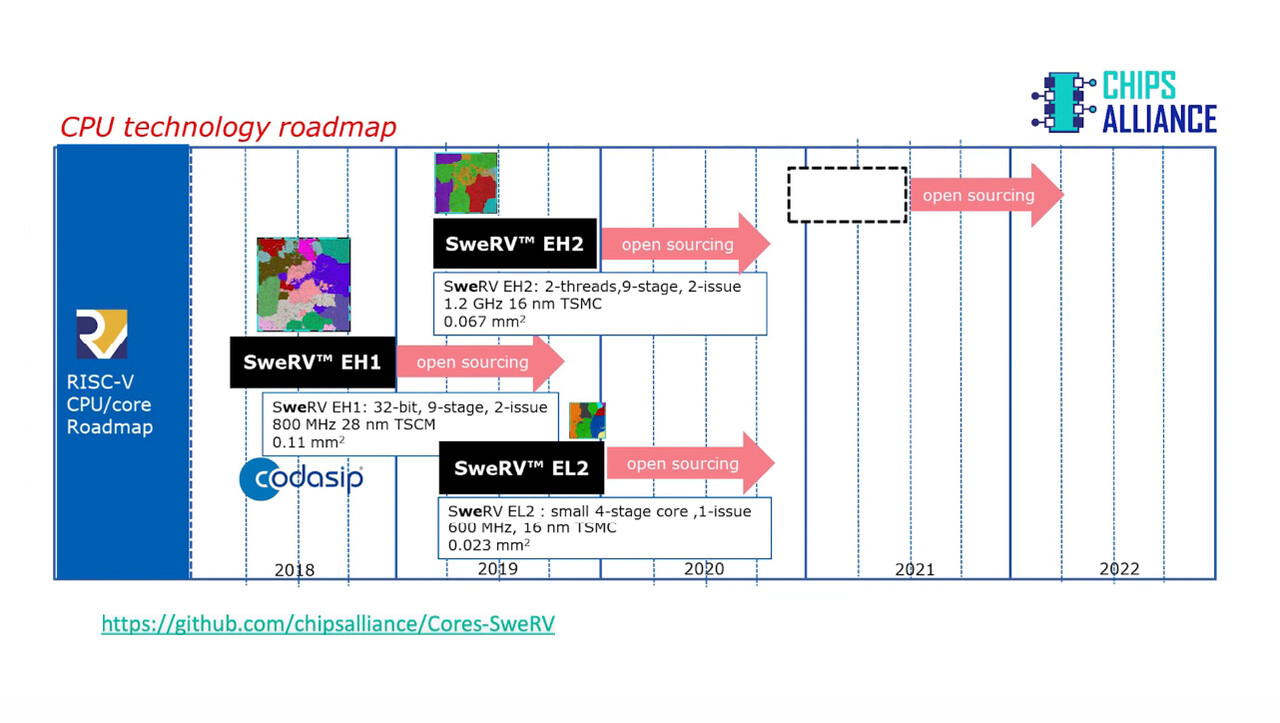

RISC-V SweRV CoreTM 系列

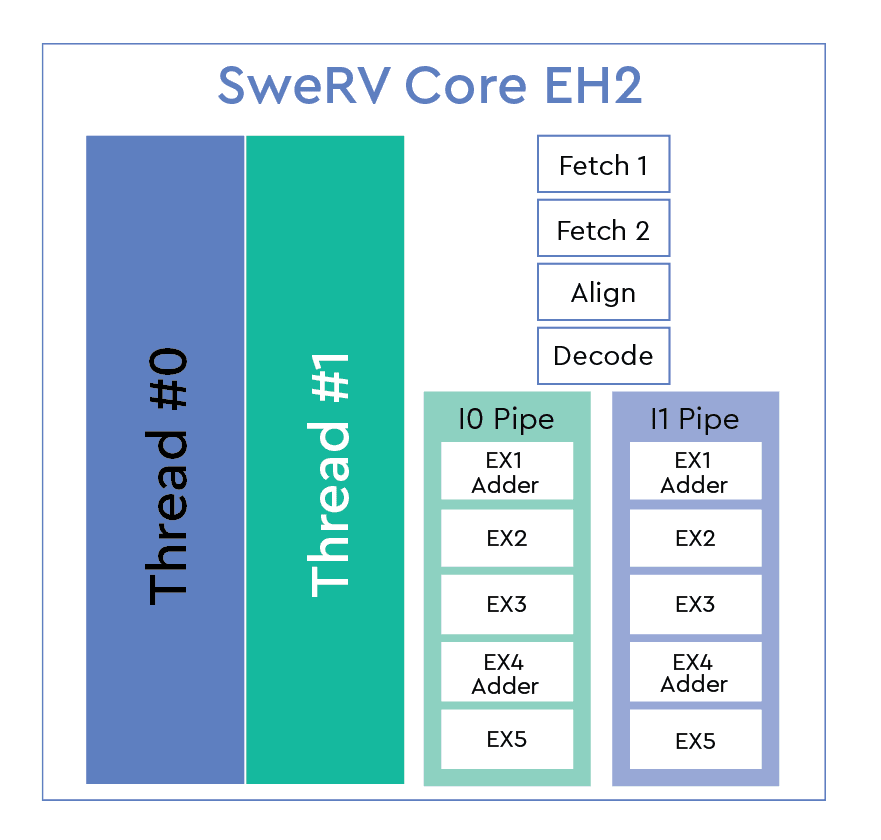

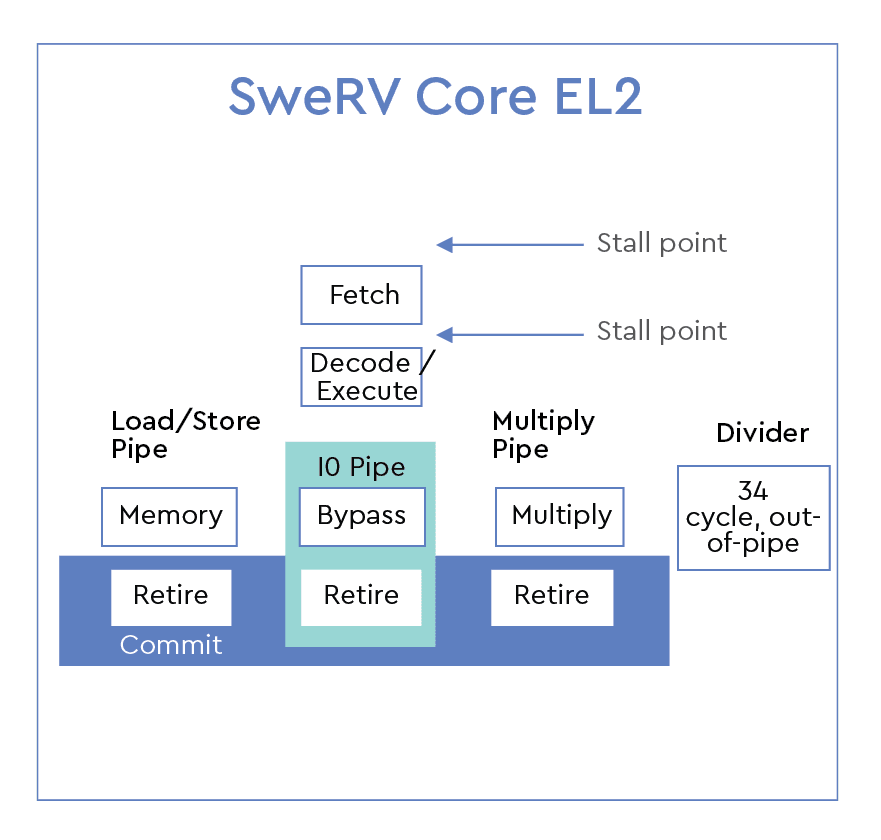

Western Digital 已开发三款 RISC-V 内核,分别是 SweRV Core EH1、EH2 和 EL2。

内核名称

线程

CoreMark/Mhz

SweRV Core EH1

单线程

4.9

SweRV Core EH2

双线程

6.3

SweRV Core EL2

单线程

3.6

Western Digital SweRV Core EH1 是一款双路超标量 32 位 9 级流水线内核。SweRV Core EH2 基于 EH1 构建,但增加了双线程功能,可进一步提高性能。最后,SweRV Core EL2 是具有中等性能的较小内核,旨在用来取代系统单芯片 (SoC) 上的状态机和其他逻辑功能。

SweRV Core 会在不久的将来用于各种 Western Digital 产品。这三个内核均已在 CHIPS Alliance Github 上开源。CHIPS Alliance 是一个开发开源硬件和开源软件设计工具的组织。它提供无障碍的协作环境,可降低 RTL 开发的成本。如需获取 SweRV Core EH1,请访问 https://github.com/chipsalliance/Cores-SweRV

如需 EH2,请访问 https://github.com/chipsalliance/Cores-SweRV-EH2

如需 EL2,请访问 https://github.com/chipsalliance/Cores-SweRV-EL2

视频

RISC-V SweRV Core 系列概览

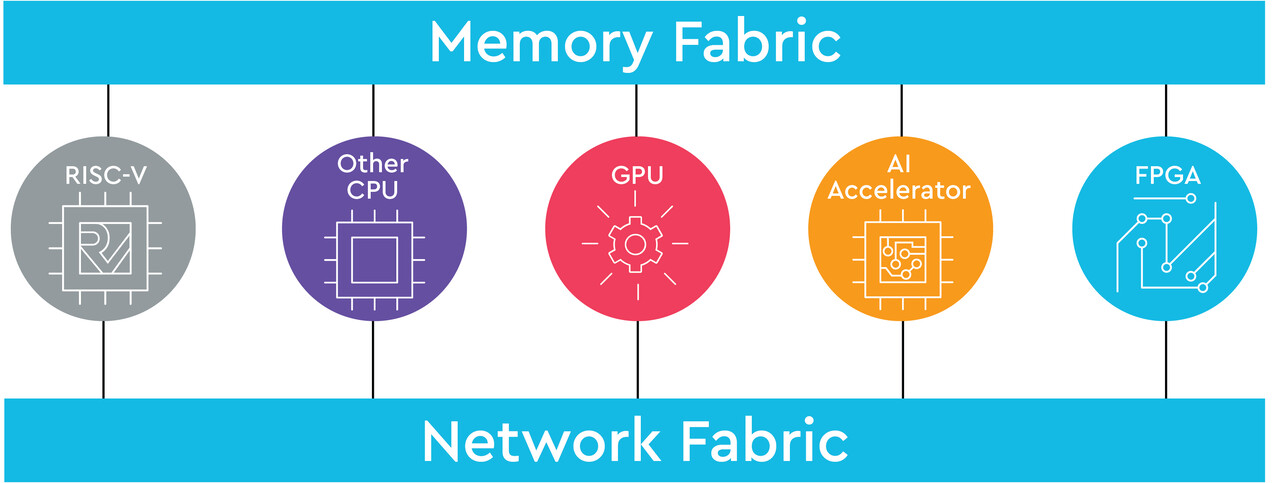

OmniXtend:通过商用结构直接缓存

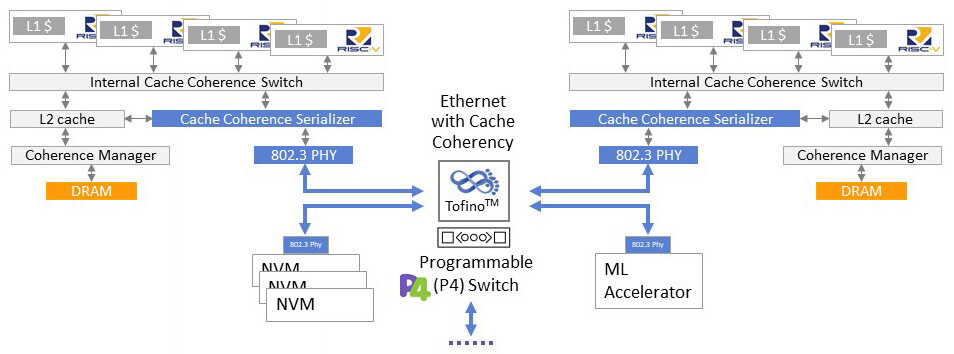

Western Digital 的 OmniXtend 是一种开放式缓存一致性协议,它利用编程设计的现代以太网交换机实现处理器缓存、内存控制器和加速器功能,从而直接通过与以太网兼容的结构交换一致性消息。它是一个真正开放的解决方案,可以将持久内存有效地附加到处理器上,并为连接计算、存储、内存和 I/O 组件的未来高级结构提供潜在支持。

OmniXtend 基于 TileLink 一致性协议构建,能够提供超出处理器芯片的性能。OmniXtend 数据平面的可编程性允许将未来对协议的改进立即部署到现场,而不需要新的系统软件或新的 ASIC。OmniXtend 未来的开发将在将再 CHIPS Alliance 组织内完成。有关详情,请访问 https://github.com/chipsalliance/omnixtend。

视频

战略创新:Western Digital 的 RISC-V

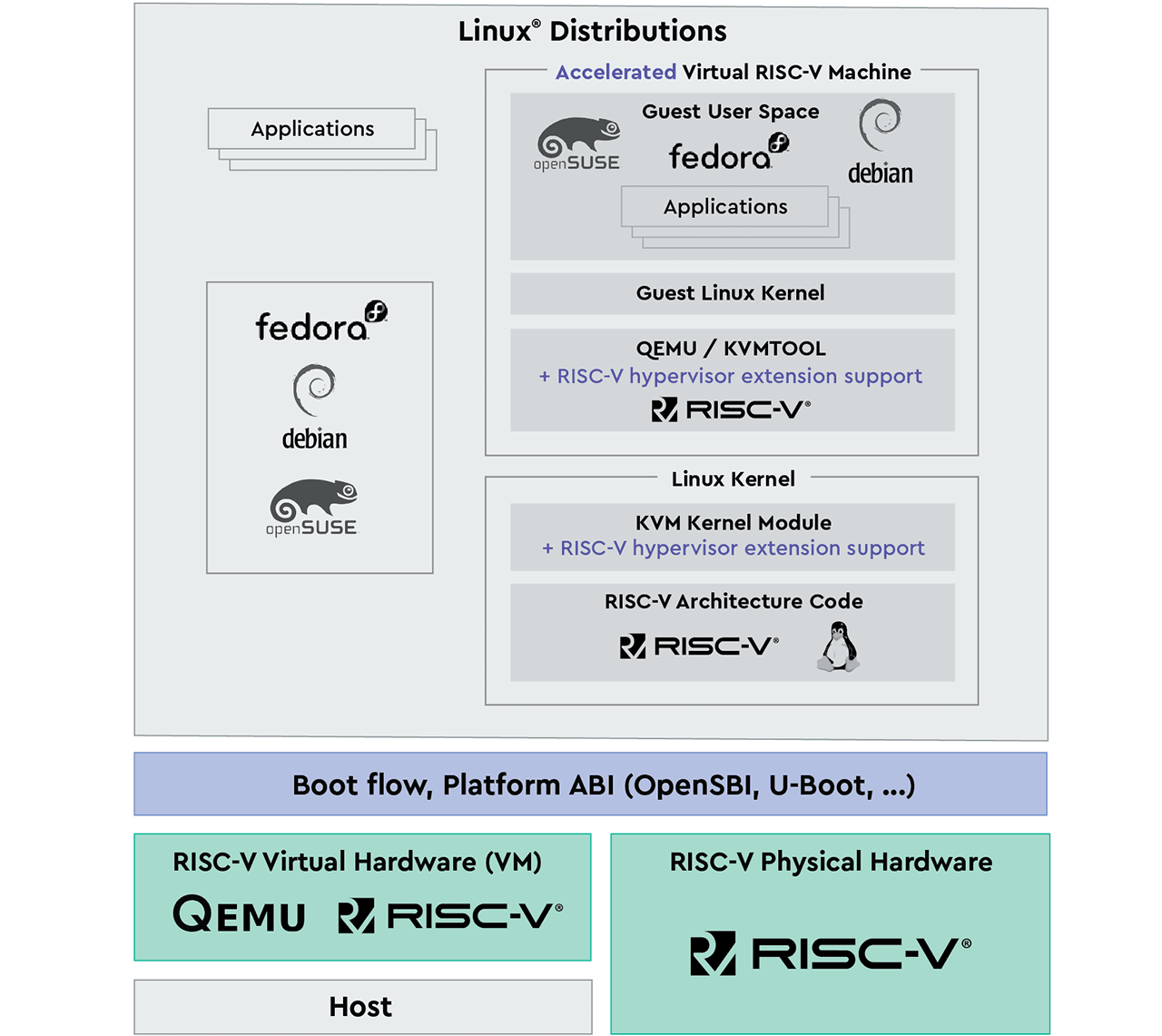

开源 RISC-V 软件

为实现快速发展,RISC-V 需要在周边构建一套完整的软件生态系统。此生态系统的组件要求非常多样化,覆盖下至低级固件和引导加载程序,上至功能齐全的操作系统内核和应用程序。其中每个组件对于确保 RISC-V 的成功,以及通过开源贡献的优势来加速构建都有重要作用。

为鼓励生态系统内的创新,Western Digital 为 Linux 社区贡献了许多内容。更多详细信息请访问 https://github.com/kvm-riscv。

精选下载

随时获取信息,造就无限可能。加快数据流动速度,促进数据繁荣发展。

为以数据为中心的新世界而创新

视频

2019 年 RISC-V 峰会:释放内存!

2020 年 1 月 15 日

Western Digital 2019 年 RISC-V 峰会主题演讲,宣布推出新的 SweRV Core 和 OmniXtend 参考设计

视频

2019 年 RISC-V 峰会:

RISC-V 和 Chips Alliance 可满足新的计算需求

2020 年 1 月 15 日

2019 年 RISC-V 峰会上的 CHIPS Alliance 主题演讲,介绍了组织和最新研发工作。

视频

2019 年 RISC-V 峰会:基于 RISC-V 的开源且具有连贯性的内存中心架构

2020 年 1 月 15 日

基于具有缓存连贯性的以太网,在 OmniXtend 的内存结构方面进行了技术更新

视频

2019 年 RISC-V 峰会:SweRV Core 路线图

2020 年 1 月 15 日

有关 Western Digital 新推出的 RISC-V SweRV Core EH2 和 EL2 的技术细节

视频

2019 年 RISC-V 峰会:置顶赞助商 Western Digital 展示了 GCC 编译器代码大小密度

2020 年 1 月 15 日

RISC-V 改进的最新 GCC 代码密度。

视频

2019 年 RISC-V 峰会:置顶赞助商 Western Digital 展示了 RISC V 的虚拟机监控程序支持

2020 年 1 月 15 日

QEMU 的技术更新和 RISC V 的虚拟机监控程序支持。

活动

RISC-V 活动

2019 年 4 月 4 日

RISC-V 基金会定期举办活动和研讨会。敬请参与您附近的活动。

视频

OmniXtend,一种开源缓存一致性内存互联结构

2019 年 6 月 12 日

Western Digital OmniXtend 概述。通过商用以太网结构直接缓存。利用此开放缓存一致性总线,异构设备现在可以平等地访问主内存。

视频

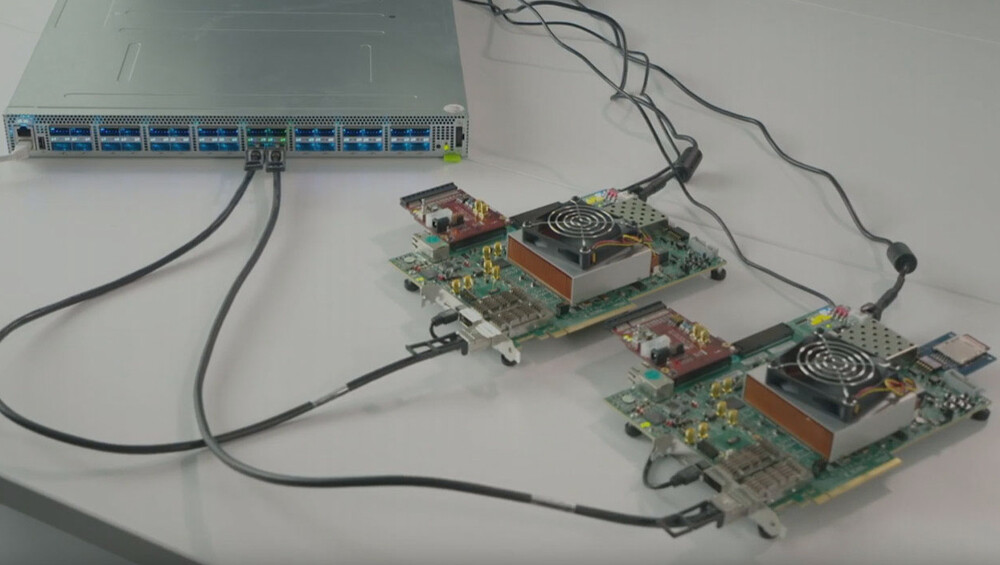

如何利用 RISC-V 和 Tofino 设置 OmniXtend 一致性内存互联结构演示

2019 年 6 月 20 日

详细介绍如何设置 OmniXtend 演示的视频。该演示使用两个 FPGA 板和一个可编程以太网交换机。它说明了 FPGA 板的编程和需要在交换机上运行的 P4 代码。

来自我们博客的精选文章

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

了解详情对 RISC-V

感兴趣?

请与我们联系。

披露

1. 基于内部测试