RISC-V: 가속화하는

차세대

컴퓨팅 요구 사항

RISC-V 에코시스템의 성장

RISC-V는 새로운 프로세서 혁신의 시대를 가능하게 하는 개방형 ISA입니다. 개방형 표준 인터페이스 및 RISC-V 처리 아키텍처를 더욱 가속화하기 위해 Western Digital은 RISC-V 에코시스템을 성장시키는 데 도움이 되는 하드웨어 및 소프트웨어 솔루션을 제공하기 위해 노력해 왔습니다.

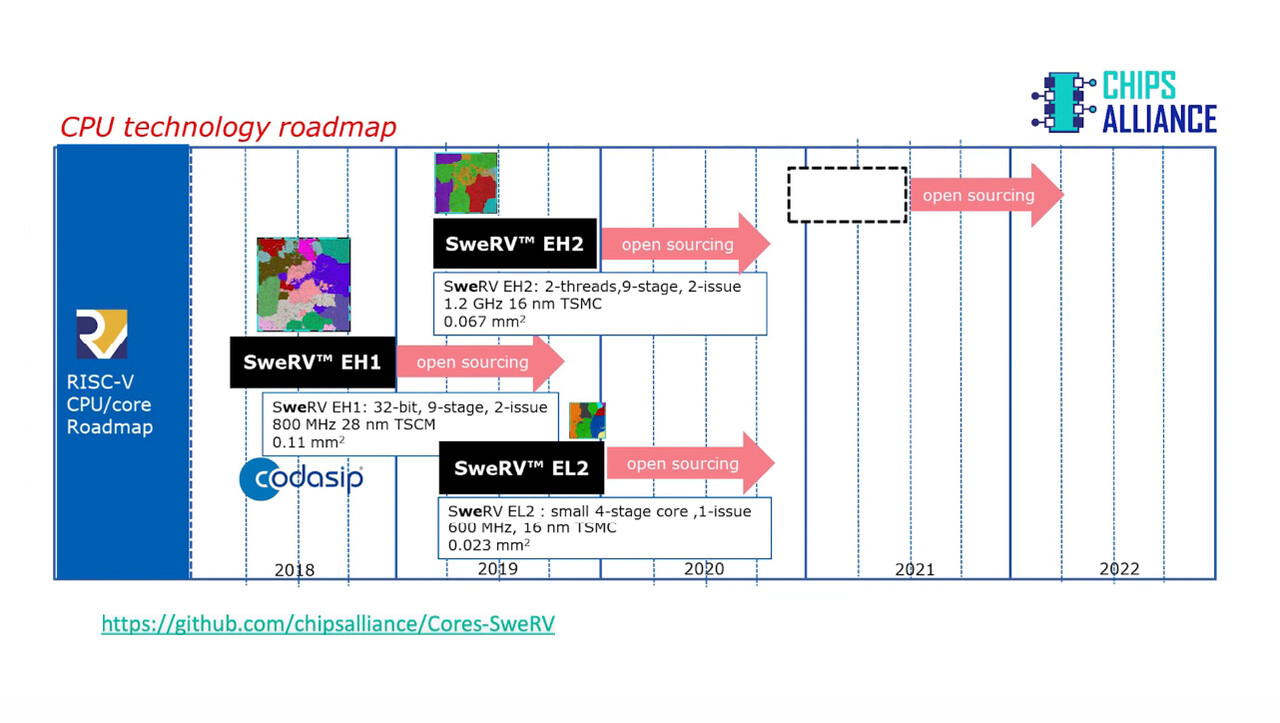

RISC-V SweRV CoreTM 제품군

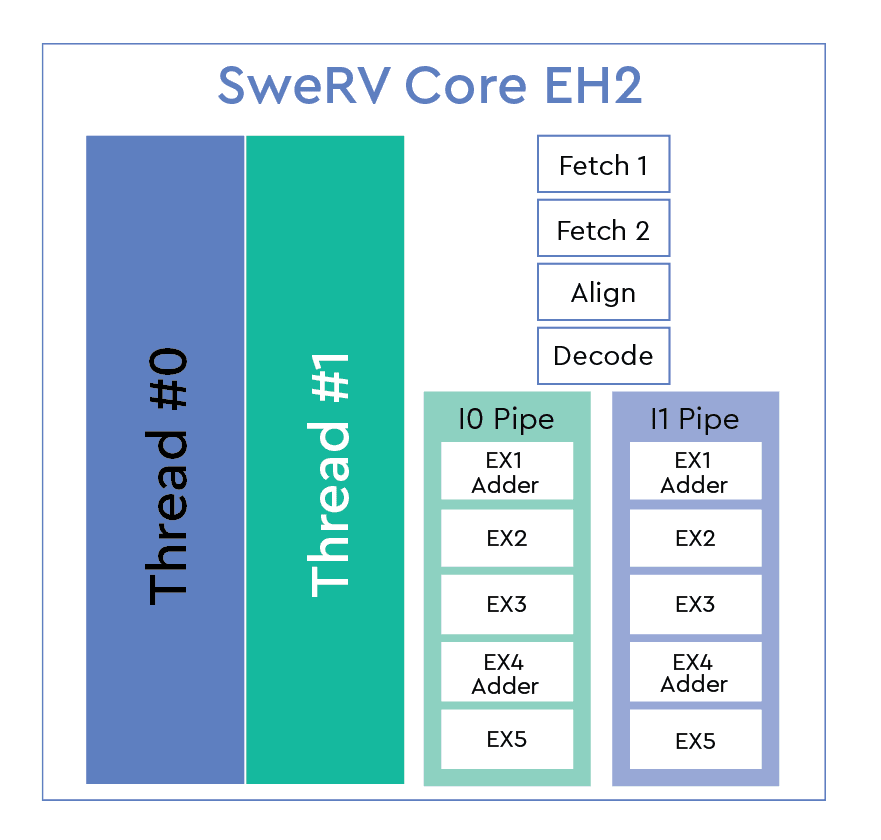

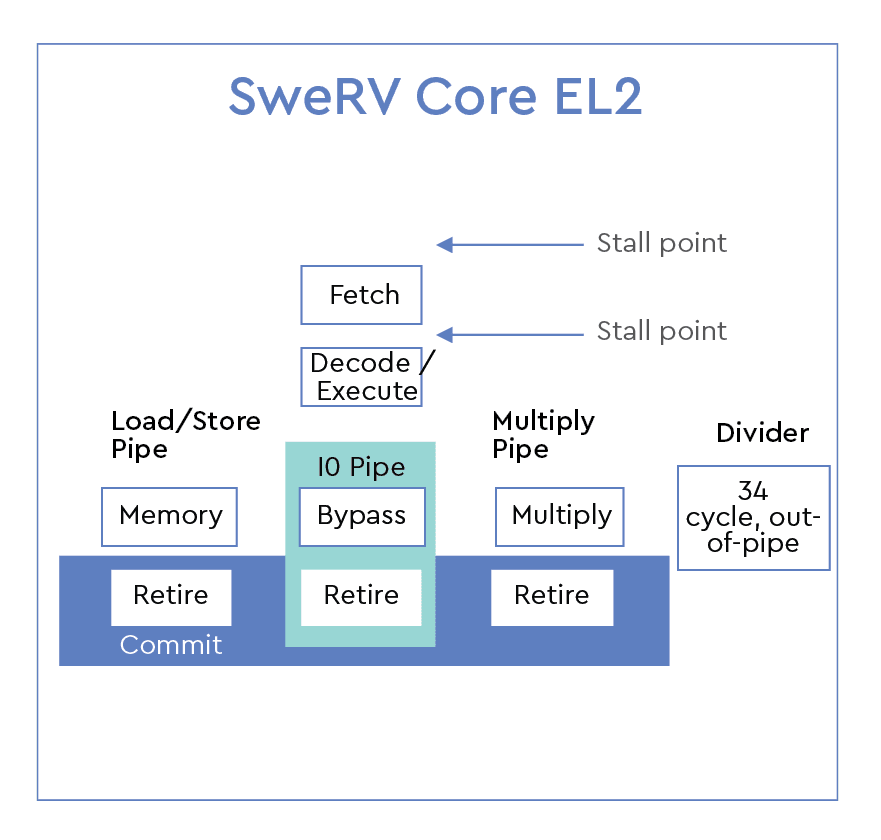

Western Digital은 다음과 같이 세 가지 RISC-V 코어인 SweRV Core EH1, EH2, EL2를 개발했습니다.

코어 이름

스레드

CoreMarks/Mhz

SweRV Core EH1

싱글

4.9

SweRV Core EH2

듀얼

6.3

SweRV Core EL2

싱글

3.6

Western Digital SweRV Core EH1은 32비트의 투-웨이 슈퍼스칼라 구조의 9단계 파이프라인 코어입니다. SweRV Core EH2는 EH1을 기반으로 제작되었지만, 이중 스레드 기능이 추가되어 성능은 더욱 향상되었습니다. 마지막으로 SweRV Core EL2는 일반적인 성능을 제공하는 작은 사이즈의 코어입니다. SoC의 상태 기계 및 기타 로직 기능을 대체하도록 설계되었습니다.

SweRV Core는 가까운 시일 내에 Western Digital의 여러 제품에 사용될 것입니다. 세 코어 제품 모두 CHIPS Alliance 깃허브에 오픈 소스로 공개되어 있습니다. CHIPS Alliance는 오픈 소스 하드웨어 및 오픈 소스 소프트웨어 디자인 도구를 개발하는 조직으로, RTL 개발 비용을 낮추기 위해 장벽 없는 협업이 이루어지고 있는 곳입니다. SweRV Core EH1은 https://github.com/chipsalliance/Cores-SweRV에서 확인할 수 있습니다.

EH2는 https://github.com/chipsalliance/Cores-SweRV-EH2에서 확인할 수 있습니다.

EL2는 https://github.com/chipsalliance/Cores-SweRV-EL2에서 확인할 수 있습니다.

비디오

RISC-V SweRV Core 제품군 개요

OmniXtend: 범용 패브릭을 통한 캐시로 직접 연결

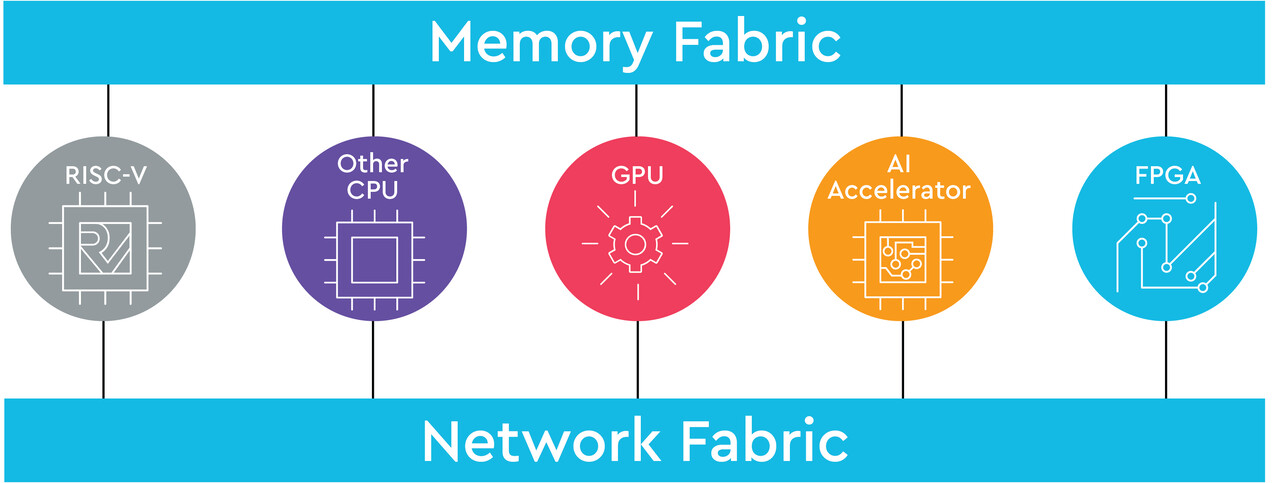

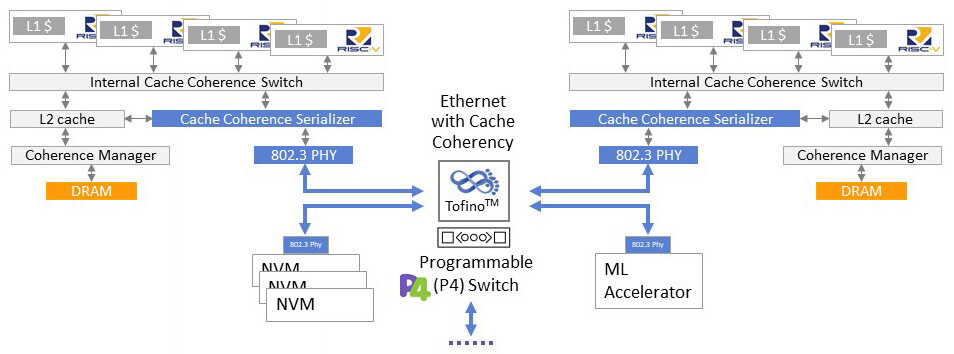

Western Digital의 OmniXtend는 최신 이더넷 스위치의 프로그래밍 기능을 활용하여 프로세서의 캐시, 메모리 컨트롤러 및 가속기가 이더넷 호환 패브릭을 통해 일관성 메시지를 직접 교환할 수 있도록 하는 개방형 캐시 일관적 프로토콜입니다. 이는 영구 메모리를 프로세서에 효율적으로 연결하기 위한 진정한 개방형 솔루션으로 컴퓨팅, 스토리지, 메모리 및 I/O 구성 요소를 연결하는 미래형 고급 패브릭에 대하여 잠재적인 지원을 제공합니다.

OmniXtend는 TileLink 일관적 프로토콜을 기반으로 프로세서 칩 이상으로 확장됩니다. OmniXtend 데이터 플레인의 프로그래밍 기능을 통해 새로운 시스템 소프트웨어나 새로운 ASIC 없이도 현장에서 즉시 프로토콜을 개선할 수 있습니다. CHIPS Alliance 조직에서 OmniXtend의 추가 개발이 이루어질 것입니다. 자세한 내용은 https://github.com/chipsalliance/omnixtend에서 확인할 수 있습니다.

비디오

전략적 혁신: Western Digital의 RISC-V

오픈 소스 RISC-V 소프트웨어

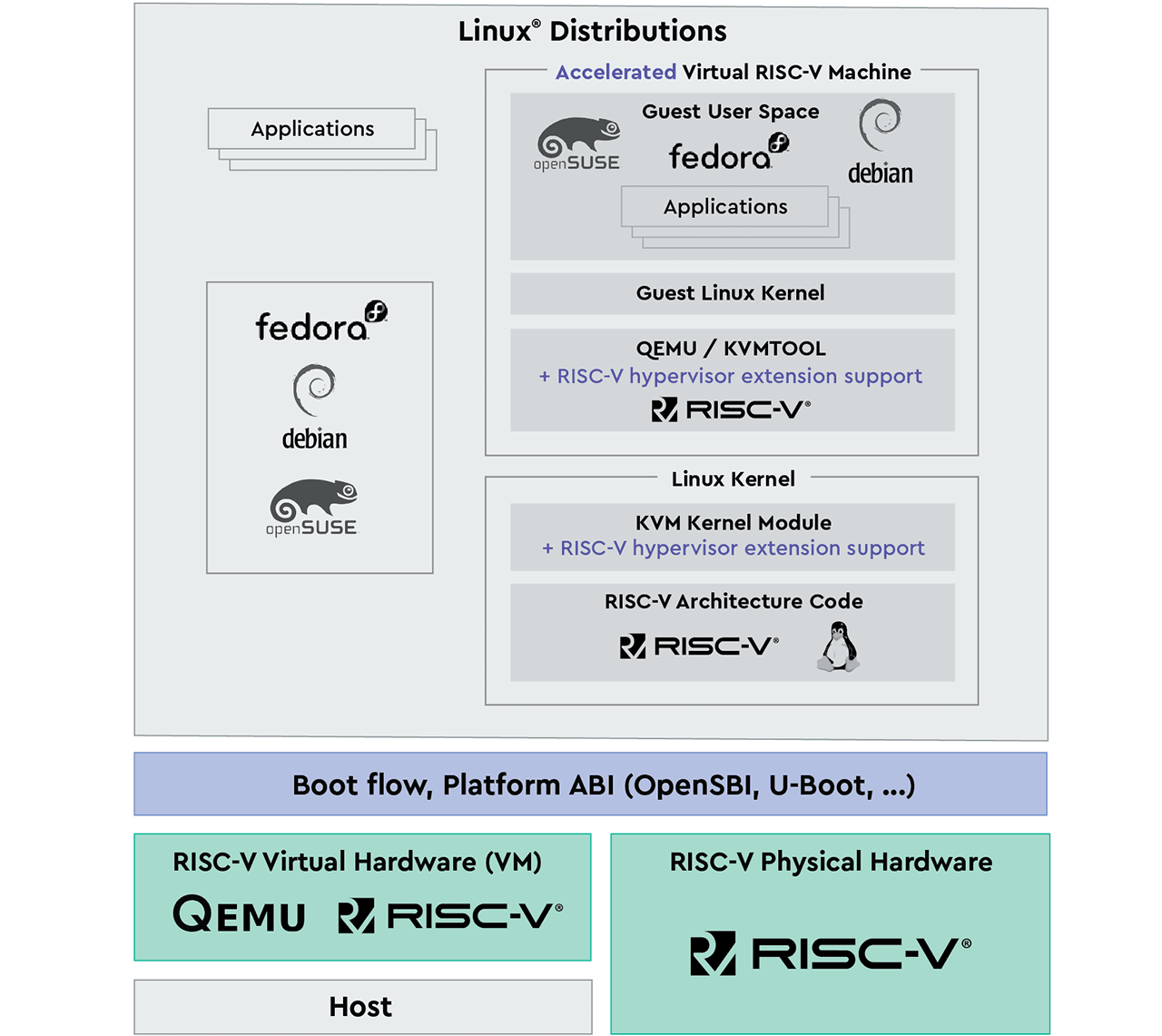

RISC-V가 더욱 확장되려면 완벽한 소프트웨어 에코시스템이 필요합니다. 에코시스템의 구성 요소는 매우 다양하여 낮은 수준의 펌웨어 및 부트 로더에서 완전한 기능을 갖춘 운영 체제 커널 및 애플리케이션에 이르기까지 모든 계층에 분산되어 있습니다. 이러한 각각의 구성 요소는 RISC-V의 성공을 보장하는 데 중요한 역할을 하며 오픈 소스의 기여를 통해 구축 시간을 단축합니다.

에코시스템의 혁신을 장려하기 위해 Western Digital은 Linux 커뮤니티에 많은 기여를 해 왔습니다. 자세한 내용은 https://github.com/kvm-riscv에서 확인할 수 있습니다.

추천 다운로드

정보에 액세스할 수 있다면 가능성은 무한합니다. 데이터 흐름을 가속화하여 데이터를 효율적으로 활용할 수 있습니다.

데이터 중심 환경을 위한 혁신

비디오

RISC-V 서밋 2019: 메모리의 한계를 극복하다

2020년 1월 15일

Western Digital 2019 RISC-V 서밋 기조연설에서 새로운 SweRV 코어 및 OmniXtend 참조 디자인 공개

비디오

RISC-V 서밋 2019:

RISC-V 및 Chips Alliance, 새로운 컴퓨팅 요구 사항 발표

2020년 1월 15일

2019 RISC-V 서밋의 CHIPS Alliance 기조연설에서 조직 및 최신 개발 노력에 대해 설명.

비디오

RISC-V 서밋 2019: RISC-V로 개방 및 일관형 메모리 중심 아키텍처

2020년 1월 15일

캐시 일관적 이더넷 기반 메모리 패브릭을 제공하는 OmniXtend의 기술적 업데이트.

비디오

RISC-V 서밋 2019: SweRV 코어 로드맵

2020년 1월 15일

Western Digital의 새로운 RISC-V SweRV 코어 EH2 및 EL2의 기술적인 세부 사항

비디오

RISC-V 서밋 2019: 헤드라인 스폰서 Western Digital, GCC 컴파일러 코드 크기 밀도 발표

2020년 1월 15일

RISC-V의 최신 GCC 코드 밀도 개선 사항.

비디오

RISC-V 서밋 2019: 헤드라인 스폰서 Western Digital, RISC V 하이퍼바이저 지원 발표

2020년 1월 15일

QEMU 및 RISC-V의 하이퍼바이저 지원에 대한 기술적 업데이트

이벤트

RISC-V 이벤트

2019년 4월 4일

RISC-V 재단에서는 정기적으로 이벤트와 워크샵을 개최합니다. 각 지역 이벤트에 참여하세요.

비디오

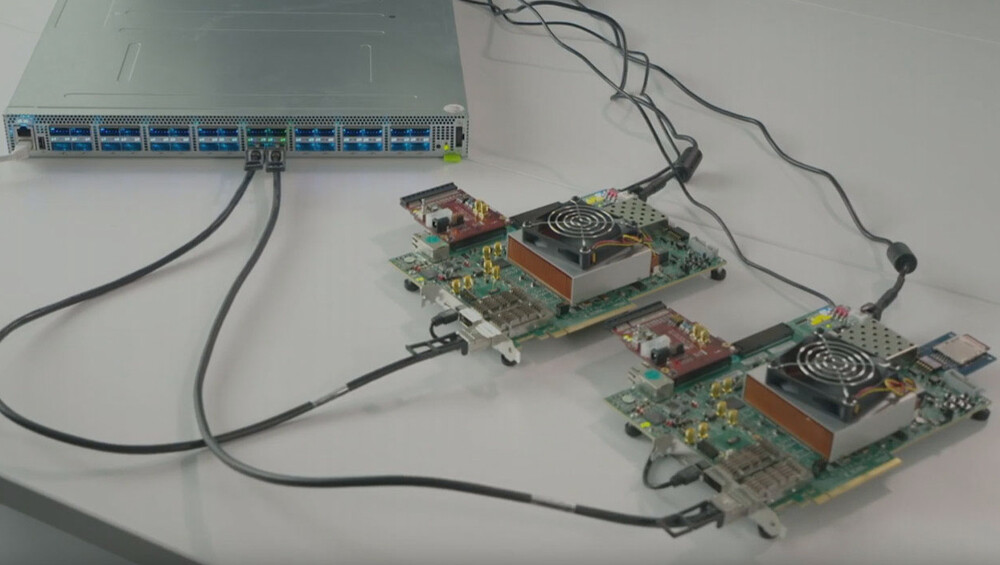

OmniXtend, 개방형 캐시 일관적 메모리 패브릭

2019년 6월 12일

Western Digital의 OmniXtend에 대한 전체적인 개요. 범용 이더넷 패브릭을 통해 캐시에 직접 연결. 이 개방형 캐시 일관적 버스를 통해 이제 이기종 장치에서 메인 메모리에 동등하게 액세스할 수 있습니다.

비디오

RISC-V 및 Tofino를 사용하여 OmniXtend 일관적 메모리 패브릭 데모 설정 방법

2019년 6월 20일

OmniXtend 데모를 설정하는 방법이 자세히 설명된 비디오. 이 데모에서는 두 개의 FPGA 보드와 프로그래밍 가능한 이더넷 스위치를 사용합니다. 또한 FPGA 보드 프로그래밍과 스위치에서 실행하는 데 필요한 P4 코드에 대해 설명합니다.

블로그의 추천 기사

{{getMergeArray(feed.title, '')}}

{{getEllipsis(getUnEscapedHTMLContent(getMergeArray(feed.description)), 180)}}

자세히 읽기

RISC-V에 관심이 있으신가요?

연결해보세요.

공개 정보

1. 이 수치는 내부 테스트를 기준으로 한 결과입니다.